摘 要

随着信息产业在我国国民经济中扮演越来越重要的角色,信息技术的发展和数据传输的安全性受到了有关部门的重视,加强网络信息安全的加密产品具有广泛的应用前景。此课题主要研究了基于ATAES132硬件描述语言的AES加密算法原理及优化,以及设计硬件实现。

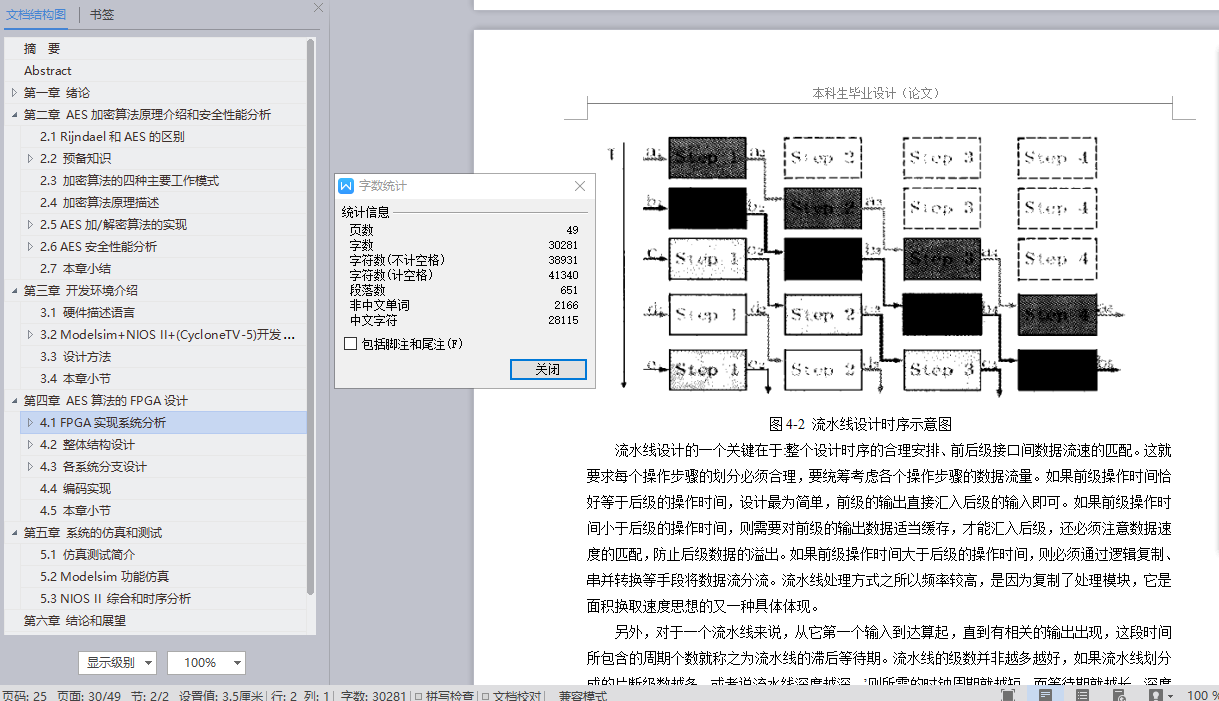

本文先介绍了先进加密算法(AES)的原理,同时讲述了其与Rijndael设计的异同。安全,高效,易拓展优化,硬件实现简单是其的特点,同时,本文还研究了算法实现的关键技术。在设计过程中,完成了整体结构的规划和各部分的端口的定义,用ATAES132语言完成了电路的RTL级的描述,同时使用了Model公司的Modelsim仿真工具进行了软件平台 上的仿真,实现了128位比特密钥的加密解密的逻辑功能,硬件上使用了基于Xilinx公司的CycloneTV系列芯片,并用NIOS II软件进行了FPGA综合,仿真基本达到了要求,这也证明了设计的正确性。在设计中尤其要提到的是本文采用了ECB(电子密码本)加密算法模式,采用流水线结构,提高了电路的工作频率和速度,本设计的创新点在于用语言实现S盒变换时,并没有采用传统的查表方式,而是直接采用了算法描述,相较之下,节省了电路的存储面积,实现了优化。

关键字: ATAES132, AES,先进加密标准,Rijndael设计,FPGA,加密,高速,流水线结构

Abstract

With the information industry playing a more and more important role in the national economy of our country, the development of information technology and the security of data transmission have received the attention of relevant departments. Encryption products that enhance the security of network information have a wide application prospect. This paper mainly studies the principle and optimization of AES encryption algorithm based on ATAES132 hardware description language and the design of hardware implementation.

This paper first introduces the principle of Advanced encryption algorithm (AES), and at the same time describes the similarities and differences between it and Rijndael design.Security, high efficiency, easy to expand and optimize, simple hardware implementation are its characteristics. At the same time, this paper also studies the key technology of algorithm implementation.In the design process, the overall structure planning and the definition of each part of the port are completed, and the RTL level of the circuit is described with ATAES132 language. At the same time, the simulation on the software platform is carried out by using the Modelsim simulation tool of Model Company.The logic function and hardware of 128-bit key encryption and decryption are realized. The CycloneTV series chip based on Xilinx company is used in this paper, and the FPGA synthesis is carried out with NIOS II software. The simulation basically meets the requirements, which also proves the correctness of the design.Especially mentioned in the design is the ECB (Electronic Cryptography) encryption algorithm mode adopted in this paper, and pipeline structure is used to improve the working frequency and speed of the circuit. The innovation of this design lies in the realization of S-box transformation in language.Instead of using the traditional lookup method, the algorithm is used directly, which saves the storage area of the circuit and realizes the optimization.

Keywords: ATAES132, AES, Advanced encryption Standard Rijndael Design FPGA, encryption, High Speed, pipeline structure

目 录

摘要 I

关键字 I

Abstract. II

Key words II

第一章 绪论 1

1.1密码学简介和我国信息安全现状 1

1.2 数据加密标准的发展过程 2

1.2.1数据加密标准DES 2

1.2.2 高级加密标准AES 2

1.3 AES的研究现状 2

1.3.1 算法的研究现状 2

1.3.2 硬件实现的研究现状 3

1.4 本论文的意义 4

1.5 内容和创新 4

1.6 本章小结 5

第二章 AES加密算法原理介绍和安全性能分析 6

2.1 Rijndael和AES的区别 6

2.2 预备知识 6

2.2.1 Rijdael的数学基础和设计思想 6

2.2.2 字节运算(位运算) 9

2.2.3 四字节运算 9

2.3 加密算法的四种主要工作模式 10

2.4 加密算法原理描述 12

2.5 AES加/解密算法的实现 13

2.5.1 S盒变换 SubBytes() 14

2.5.2 行变换ShiftRows() 15

2.5.3 列变换Mixcolumns() 15

2.5.4 与扩展密钥的异或运算AddRoundKey() 16

2.5.5 密钥扩展程序 Key Expansion( ) 16

2.6 AES安全性能分析 16

2.6.1安全性原则 17

2.6.2 AES算法的安全性 17

2.6.3AES算法的性能分析 18

2.7 本章小结 18

第三章 开发环境介绍 20

3.1 硬件描述语言 20

3.2 Modelsim+NIOS II+(CycloneTV-5)开发环境 20

3.2.1 Modelsim 20

3.2.2 逻辑综合和综合工具NIOS II 21

3.2.3 Xilinx CycloneTV-5系列FPGA 22

3.3 设计方法 23

3.4 本章小节 24

第四章 AES算法的FPGA设计 25

4.1 FPGA实现系统分析 25

4.1.1 软硬件实现方法比较 25

4.1.2 性能参数 26

4.1.3 关键技术 26

4.2 整体结构设计 28

4.2.1 总体设计方案 28

4.2.2 总体系统结构框图 30

4.3 各系统分支设计 31

4.3.1 加解密模块的设计 31

4.3.2 控制模块设计 33

4.3.3 密钥扩展模块设计 34

4.3.4 接口模块设计 35

4.4 编码实现 36

4.5 本章小节 36

第五章 系统的仿真和测试 38

5.1 仿真测试简介 38

5.2 Modelsim功能仿真 38

5.3 NIOS II 综合和时序分析 43

第六章 结论和展望 44

致谢 45

参考文献 46