|

;">硬件描述语言(HDL)是一种用形式化方法描述数字电路和系统语言。利用这种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下来,利用现场可编程门阵列FPGA自动布局布线工具,把网表转换成要实现的具体电路布线结构。

目前,这种高层次(High-Level-Design)的方法已被广泛采用。据统计,目前在美国的硅谷约有90%以上的FPGA采用硬件描述语言进行设计。硬件描述语言HDL的发展至今已有20多年的历史了,并成功应用于EDA设计的各个阶段:建模、仿真、验证和综合等。到20世纪80年代,已经出现了上百种硬件描述语言,对设计自动化曾起到极大的促进和推动作用。但是,这些语言一般各自面向特点的设计领域和层次,而且众多的语言使用户无从适应。因此,急需一种面上设计的多领域、多层次并得到普遍认同的标准硬件描述语言。20世纪80年代后期,VHDL和Verilog HDL语言适应这种趋势的要求,先后成为IEEE标准。

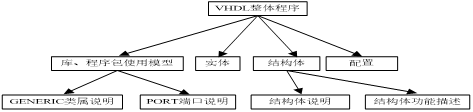

本设计采用VHDL作为硬件描述语言,因为VHDL能够形象化地表示出电路的结构与行为,支持从系统到逻辑门级所有层次的设计,适合复杂电路和系统设计,除此之外它还是与显示技术相独立的语言,既不束缚于某一特定模拟程序或数字装置,也不把设计方法强加于设计者。其最大的特点是描述能力强,可覆盖逻辑设计的诸多领域和层次,并支持众多硬件模型。因此我们选用VHDL作为DDS设计的硬件描述语言。VHDL程序设计的基本结构如图2-6所示

图2-6 VHDL程序基本结构图

3综合设计

3.1 FPGA设计部分

此设计中,FPGA需要完成DDS模块、DDS顶层设计模块、DDS波形存储器模块和DDS接口测试模块的设计。

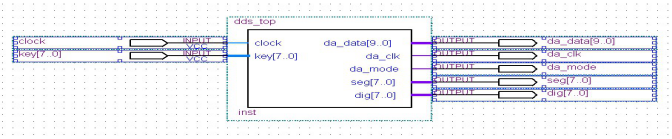

3.1.1 DDS顶层模块的设计

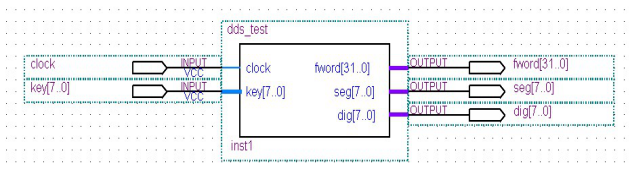

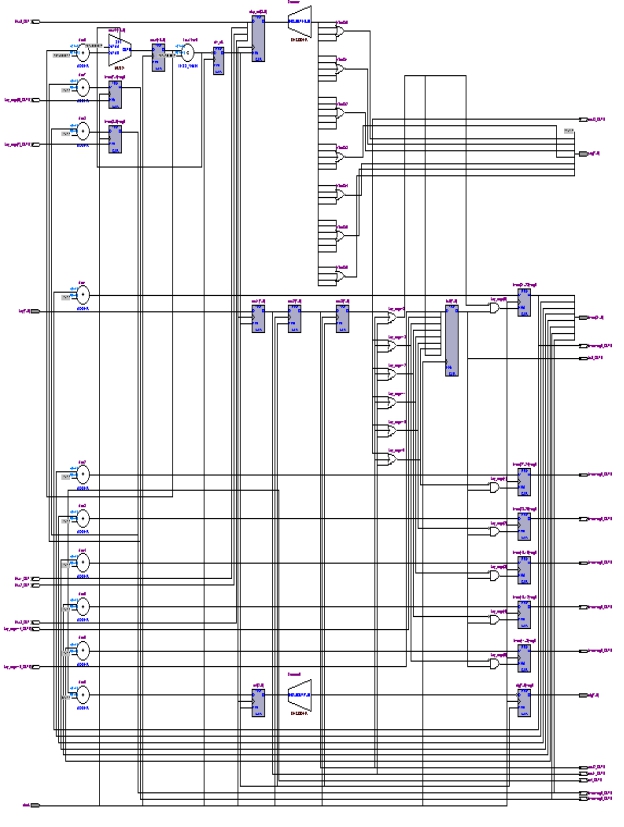

此模块是整个设计总模块,在此模块中不仅有调用其他模块的声明,而且还有整个设计中所有管脚的定义,它是整个程序的主函数,其他所有的功能模块都是在它的控制下进行工作的,这是整个设计的核心。DDS顶层模块生成的原理图如下:

图3-1 DDS顶层模块原理图

此模块程序代码见附录1

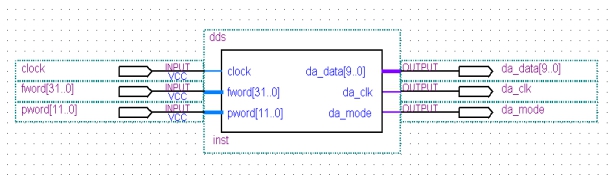

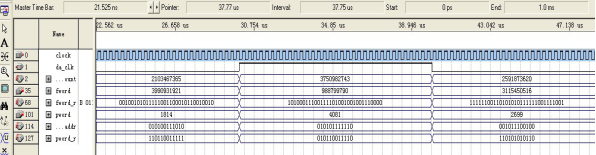

3.1.2 DDS功能模块设计

在此模块中主要设计了频率相位累加器和相位调制器,相位累加器是此设计的关键功能模块,它的性能直接决定了此设计的系统性能,相位累加主要是利用频率控制字和相位控制字来累加出寻址地址,freq_count<=freq_count + fword_r;其中fword_r位频率控制字;freq_count为寻址地址。得出的地址再从DDS波形存储器中,找到相应的波形值,然后输出,从而控制输出波形的频率。相位调制器的输入端为相位累加器的相位输出,在这里设定一个相位偏移量,是为了实现对输出信号的相位调节,如果不使用此功能,可以将此处设定为固定的数值,或者直接去掉。DDS模块生成的原理图如下:

图3-2 DDS模块生成的原理图

此模块程序代码见附录2

频率相位累加器和相位调制器的进程代码如下:

PROCESS(clock) --频率相位累加器

BEGIN

IF RISING_EDGE(clock) THEN

freq_count<=freq_count + fword_r;

END IF;

END PROCESS;

PROCESS(clock) --相位调制器

BEGIN

IF RISING_EDGE(clock) THEN

rom_addr<=freq_count(31 DOWNTO 20) + pword_r;

END IF;

END PROCESS;

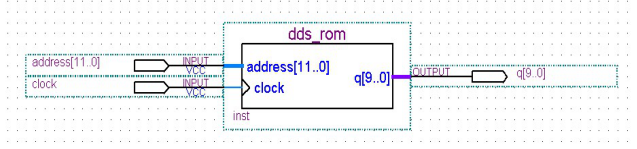

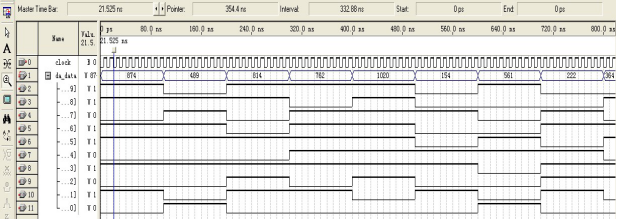

3.1.3 DDS波形存储器模块的设计

DDS波形存储器(又称正弦ROM查找表),其功能是把存储在相位累加器中的抽样值转换成正弦波幅度的数字量函数,通俗的讲,是把相位转化成幅度。本设计中,DDS的输出为10位,相比于传统的的8位输出精度提高了4倍,大大调高了产品的性能。它的输入端为相位累加器的输出端,输出端将正弦幅度信号送往DA转换器,转化为模拟信号。DDS波形存储器模块生成的原理图如下:

图3-3 DDS波形存储器模块原理图

3.1.4 DDS接口测试模块的设计

在此模块中,主要有时钟分频部分、按键检测检测部分和数码管显示部分。接口测试模块生成的电路原理图如下:

图3-4 DDS接口测试模块原理图

此模块程序代码见附录3

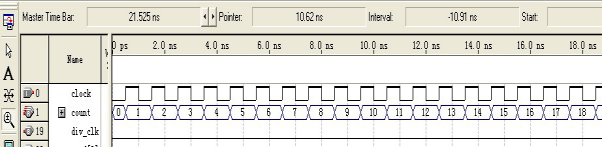

3.1.4.1 时钟分频器的设计

本设计中,系统的时钟频率为48MHz,此设计中要用到120KHz的频率,本模块的功能将clock端口输入的时钟信号分频后送给div_clk端口,利用加法器,并且对时钟频率计数器count中的数值与我们之前设定的数值进行比较,当count小于我们设定的数值时,进行加1操作,且将输出端div_clk置零,若不小于我们之前设定的数值,则将时钟频率计数器清零,且将输出端div_clk置一,由此得到我们所需要的频率,分频器的进程代码如下:

PROCESS(clock) --时钟分频部分

BEGIN

IF RISING_EDGE(clock) THEN

IF count<X"1D4C0" THEN--120000

count<=count+1;

div_clk<='0';

ELSE

count<=B"0_0000_0000_0000_0000";

div_clk<='1';

END IF;

END IF;

END PROCESS;

3.1.4.2 按键检测部分设计

此设计中利用八个按键KEY1~KEY8控制输入DDS的频率字,从而控制输出波形的频率,当按下一个键时,对该位进行加1操作,位权为16,当满16时,该位清零,高一位不加1,这样设计是为了方便用户操作,减小操作难度。设计中,先对按键进行消抖操作,保证输入的准确性。按键消抖进程代码如下:

PROCESS (clock)--<<按键消抖部分

BEGIN

IF RISING_EDGE(clock) THEN

IF div_clk='1' THEN

dout1<=key;

dout2<=dout1;

dout3<=dout2;

END IF;

END IF;

END PROCESS;

消抖检测后,还需要对按键进行边沿检测,进一步保证输入的准确性,其进程代码如下:

PROCESS (clock)--按键边沿检测部分

BEGIN

IF RISING_EDGE(clock) THEN

buff<=dout1 OR dout2 OR dout3;

END IF;

END PROCESS;

key_edge<=NOT (dout1 OR dout2 OR dout3) AND buff;

具体按键操作以KEY1为例,其他的键的代码与之类似,只是存储地址不同,KEY1键的进程代码如下:

PROCESS(clock)--按键1

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(0)='1' THEN--下降沿检测

fword_r(31 DOWNTO 28)<=fword_r(31 DOWNTO 28) + 1;

END IF;

END IF;

END PROCESS;

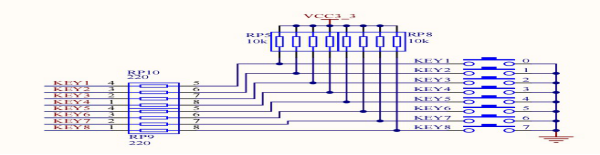

按键的硬件电路如下:

图3-5 按键电路

3.1.4.3数码管显示部分设计

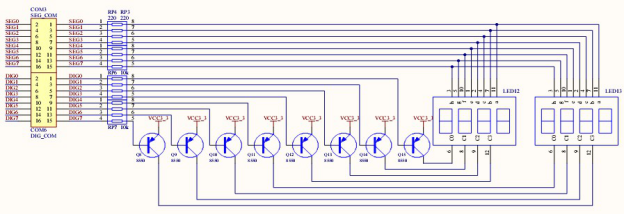

当键盘输入频率控制字时,我利用数码管1-8来分别显示8个按键的操作结果,其硬件电路图如下:

图3-6 数码管显示电路

此模块其显示程序代码见附件3

FPGA设计总体RTL电路图见附件4

3.2 外围电路设计

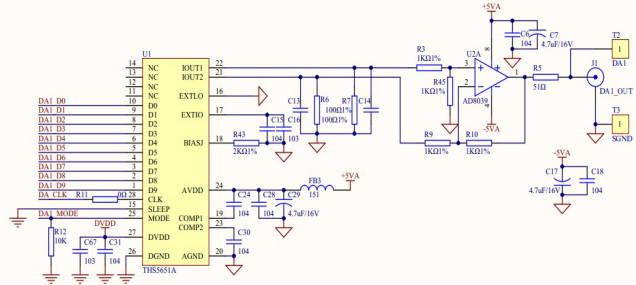

3.2.1 D/A转换电路设计

在本设计中,DDS波形存储器的输出为10位,所以我们需要一个高速的10为D/A转换器来完成数模转换,因此我们选用的是TI公司的125MS/S单路10位器件THS5651A,该器件有引脚兼容的更高速(200MS/S)器件DAC900,该芯片完全可以满足我们的性能参数要求,其硬件电路如图所示:

图3-7 D/A转换电路

3.2.2 低通滤波器的设计

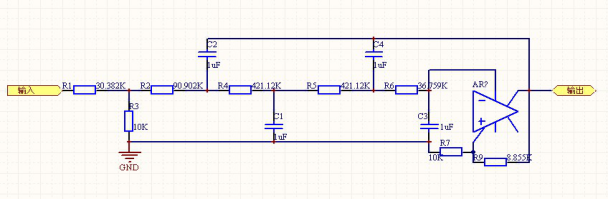

D/A输出后,通过滤波电路、输出缓冲电路,使信号平滑且具有负载能力。滤波采用二阶巴特沃兹低通滤波器,其幅度函数是单调下降的,且n阶巴特沃兹低通滤波器的前(2n-1)阶导数在ω=0处为零,所以它又称为最大平坦幅度滤波器。由于本设计要求滤波的分量主要为由D/A产生的高频分量,和要保留的频率(小于20KHZ)相差很远,所以滤波器在通带内的平坦程度比其衰减陡度更为重要。另外,巴特沃兹低通滤波器也不像其它滤波器对元件值要求那么苛刻,因为在截止频率附近,频率响应钝化可能是这些滤波器在要求锐截止的地方不合要求。设计中主要是频率为≤20KHZ的正弦波。

正弦波的输出频率小于20.48KHZ,为保证20.48KHZ频带内输出幅度平坦,又要尽可能抑制谐波和高频噪声。电路如图3-8所示:

图3-8 低通滤波器

3.2.3电源设计

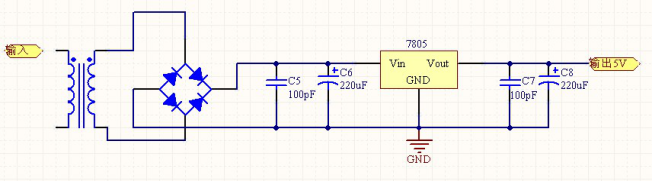

本设计需要3.3V电源和5V电源。

5V电源的设计利用稳压模块LM7805用来提供相应的电压5V,电路图3-9所示

图3-9 5V电源电路

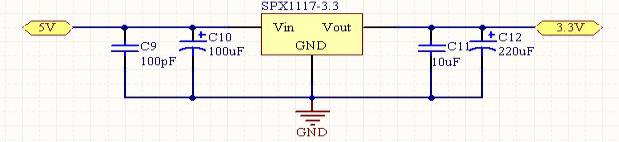

3.3V电源由5V电源经过3.3V LDO芯片SPX1117-3.3并且滤波以后得到。3.3V用于给FPGA所有I/O口、核心板上存储电路、串行配置器件、复位电路等供电。SPX1117系列LDO芯片输出电流可达800mA,输出电压精度在1%以内,还具有电流限制和热保护功能。使用时,其输出端需要接一个至少10uF的钽电容来改善瞬态响应和稳定性。电路图如图3-10所示

图3-10 3.3V电源电路

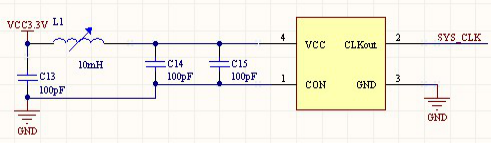

3.2.4 时钟电路的设计

FPGA内部没有振荡电路,使用有源晶振是比较理想的选择。EP1C6Q240的输入的时钟频率范围为15.625―387MHz,经过内部PLL电路后可输出15.625―275MHz的系统时钟。当输入时钟频率较低时,可以使用FPGA的内部PLL调整FPGA所需的系统时钟,使用系统运行速度更快。此设计利用48MHz的有源晶振作为系统的时钟源,为了得到一个稳定、精确的时钟频率,有源晶振的供电电源经过了LC滤波,电路图如3-11所示:

图3-11 时钟电路

4 设计的实现与仿真

本设计是在EDA设计平台上实现系统的仿真,所以需要的装置主要有PC机和Altera公司的QuartusⅡ软件。Altera公司的QuartusⅡ软件是一款易于使用的开发工具,其界面友好,集成化程度高。可通过QuartusⅡ图形编辑器创建图形设计文件(.gdf),通过QuartusⅡ文本编辑器使用VHDL语言创建文本设计文件(.vhd),还可以通过QuartusⅡ波形编辑器创建波形设计文件(.wdf)。通过QuartusⅡ编译器完成,可检查项目是否有错,并对项目进行逻辑综合,然后配置到一个ALTERA器件中,同时产生报告文件、编程文件和用于时间仿真的输出文件。

4.1 系统的编译

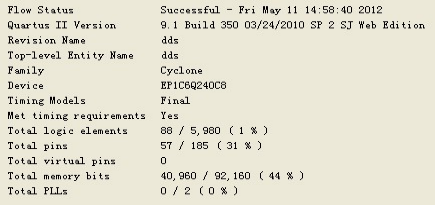

FPGA设计完成后进行编译,编译结果为图4-1所示:

图4-1编译结果

可以看出,此设计仅仅使用了1%的逻辑单元资源、318%的器件引脚,没有用到锁相环。

4.2 系统的仿真

利用QuartusⅡ软件对设计直接进行仿真验证,首先先建立一个仿真文件Vector Waveform File,然后将设计的端口导入仿真窗口,设定输入波形,进行功能仿真和时序仿真。通过QuartusⅡ软件进行仿真设定后得到分频,累加器和正弦波的仿真如图:

图4-2分频仿真

图4-3累加器仿真

图4-4正弦波的仿真

由上图可以分析出此系统符合设计的逻辑关系,完成了设计任务。

4.3 管脚分配

将设计中定义的管脚分配到FPGA硬件资源上,分配如下

|

信号

|

引脚

|

信号

|

引脚

|

信号

|

引脚

|

|

Seg[0]

|

169

|

Dig[5]

|

216

|

da�_data[2]�

|

41

|

|

Seg[1]

|

170

|

Dig[6]

|

213

|

da�_data[3]�

|

23

|

|

Seg[2]

|

167

|

Dig[7]

|

214

|

da�_data�[4]

|

20

|

|

Seg[3]

|

168

|

Key[0]

|

121

|

da�_data�[5]

|

18

|

|

Seg[4]

|

165

|

Key[1]

|

122

|

da�_data�[6]

|

16

|

|

Seg[5]

|

166

|

Key[2]

|

123

|

da�_data�[7]

|

14

|

|

Seg[6]

|

163

|

Key[3]

|

124

|

da�_data�[8]

|

13

|

|

Seg[7]

|

164

|

Key[4]

|

143

|

da�_data�[9]

|

46

|

|

Dig[0]

|

160

|

Key[5]

|

141

|

da_clk

|

38

|

|

Dig[1]

|

159

|

Key[6]

|

158

|

da�_mode

|

8

|

|

Dig[2]

|

162

|

Key[7]

|

156

|

clock

|

28

|

|

Dig[3]

|

161

|

da�_data�[0]

|

45

|

|

|

|

Dig[4]

|

215

|

da�_data�[1]

|

43

|

|

|

按照上表分配好管脚后,再进行一次编译,编译完成后,下载到FPGA芯片上。

5 总结与展望

本设计是以FPGA芯片为开发载体,以硬件描述语言VHDL为设计语言,以EDA软件工具QuartusⅡ为开发环境,运用DDS频率合成新思路来进行设计的。主要完成了一下工作:

1. 阐述了DDS的基本概念和原理,详细介绍了DDS设计方法。

2. 介绍了利用FPGA芯片运用DDS原理进行信号源的设计思路和方法。

3. 简要介绍了开发环境和设计语言。

4. 利用设计语言VHDL完成了DDS功能和外部测试功能的设计,包括DDS顶层模块、DDS功能模块、DDS波形存储器和DDS接口测试电路的设计。

5. 完成了外部相关电路的设计,包括时钟电路、电源电路、D/A转换电路、低通滤波器等的相关设计。

6. 对FPGA设计进行编译、调试、仿真和测试,找出设计的不足,加以改进。

在电子技术日新月异的发展的今天,利用EDA手段进行设计已成为不可阻挡的趋势。自上而下的设计相对于传统至底向上的设计方式具有其显著的优越性。利用EDA设计软件辅助设计和仿真,方便快捷,减少了错误率的产生,缩短了产品的设计及上市周期,既减轻了设计工作量又满足了商业利益的需求,市场前景十分广阔。

参考文献

[1]周立功.EDA实验与实践[M].北京航空航天大学出版社,2007,9:195

[2]李洪伟,袁斯华.基于QuartusⅡ的FPGA/CPLD设计[J].电子工业出版社,2006,4(1):18-20.

[3]雷伏容,李俊,尹霞.EDA技术与VHDL程序开发基础教程[M].清华大学出版社,2010,5:46.

[4]刘福奇.FPGA嵌入式项目开发实战[M].电子工业出版社2009,4:283

[5]姜萍,王建新,吉训生.FPGA实现的直接数字频率合成器[J].电子工业出版社,2002,2

[6]邵正途,高玉良.DDS/FPGA在信号产生系统中的应用[J].电子技术,2005,(1): 82

[7]傅玉朋,李明浩,吕进华.DDS技术的FPGA设计与实现.大连民族学院学报, 2004,6(3):46-47

[8]余孟尝.数字电子技术基础简明教程.高等教育出版社,2009,7:424-447

[9]周峻峰,陈涛.基于FPGA的直接数字频率合成器的设计与实现[J]. 2003,(1):4-6

[10]全国大学生电子设计竞赛组委会编.第五届全国大学生电子设计竞赛获奖作品选编(2001)[J].北京理工大学出版社,2003:1~40

[11]文卓然.数字式移相信号发生器中的一个误区.电子世界,2004,(5): 42-43

[12]贾方亮,赵泳,郝立果,张锡鹃.高精度数字式移相信号发生器的研制[J].天津职业技术师范学院学报,2004,14(2):23~25

[13周正干,李和平,李然.超低频移相信号发生器的设计[M]. 200, 0(1):9-11

致谢

在论文即将完成之际,首先要对孙红艳老师表示最真挚的感谢。在论文的写作期间,孙老师在百忙之中抽出时间指导我的论文写作,在很多关键的知识点上进行了讲解疏通,讲解了许多信号方面的专业知识,为我的论文的写作提供了强大的理论基础,同时给我论文写作的宏观框架提出了宝贵的意见,特别是由于我今年忙完其他事情后,论文写作的时间比较仓储,为了能够顺利完成论文的写作,孙老师特别为我安排了实验室,给我们提供写论文和做设计的环境。我在论文写作之初,对很多的东西还比较陌生,孙老师特别给我们推荐了参考书籍,为我的论文写作提供了知识基础,感谢她无私的帮助。由于本人学识有限,加之时间仓促,文中不免有错误和待改进之处,真诚欢迎各位师长、同学提供宝贵的意见。

附录

附录1:DDS顶层模块程序代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY dds_top IS

PORT(

clock: IN STD_LOGIC;--系统时钟

key: IN STD_LOGIC_VECTOR(7 DOWNTO 0);--按键输入

da_data:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--DA数据输出

da_clk: OUT STD_LOGIC;--DA时钟输出

da_mode:OUT STD_LOGIC;--DA模式选择输出

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管段码输出。

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管位码输出。

);

END;

ARCHITECTURE one OF dds_top IS

COMPONENT pll--调用PLL模块声明.

PORT

(

inclk0 : IN STD_LOGIC := '0';

c0 : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT dds--调用DDS模块声明.

PORT(

clock: IN STD_LOGIC;

fword: IN STD_LOGIC_VECTOR(31 DOWNTO 0);--输入频率字

pword: IN STD_LOGIC_VECTOR(9 DOWNTO 0);--输入相位字

da_data:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--输出DA数据

da_clk: OUT STD_LOGIC;--输出DA时钟

da_mode:OUT STD_LOGIC--DA模式控制

);

END COMPONENT;

COMPONENT dds_test

PORT(

clock: IN STD_LOGIC;--系统时钟48MHz

key: IN STD_LOGIC_VECTOR(7 DOWNTO 0);--按键输入key1 ~key5

fword: OUT STD_LOGIC_VECTOR(31 DOWNTO 0);--要发送的数据。

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管段码输出。

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管位码输出。

);

END COMPONENT;

SIGNAL fword: STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL dds_clk: STD_LOGIC;--pll输出时钟.

BEGIN

U1: pll PORT MAP(inclk0=>clock,c0=>dds_clk);--调用PLL模块

U2: dds PORT MAP(clock=>dds_clk,fword=>fword,pword=>X"000",da_clk=>da_clk,da_data=>da_data,da_mode=>da_mode);--调用DDS模块.

U3: dds_test PORT MAP(clock=>clock,key=>key,fword=>fword,seg=>seg,dig=>dig);--

END;

附录2DDS模块程序代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY dds IS

PORT(

clock: IN STD_LOGIC;

fword: IN STD_LOGIC_VECTOR(31 DOWNTO 0);--输入频率字

pword: IN STD_LOGIC_VECTOR(11 DOWNTO 0);--输入相位字

da_data:OUT STD_LOGIC_VECTOR(9 DOWNTO 0);--输出DA数据

da_clk: OUT STD_LOGIC;--输出DA时钟

da_mode:OUT STD_LOGIC--DA模式控制

);

END;

ARCHITECTURE one OF dds IS

COMPONENT dds_rom --调用元器件说明。

PORT

(

address : IN STD_LOGIC_VECTOR (11 DOWNTO 0);

clock : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0)

);

END COMPONENT;

SIGNAL fword_r: STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL pword_r: STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL freq_count: STD_LOGIC_VECTOR(31 DOWNTO 0);--频率相位累加器

SIGNAL rom_addr:STD_LOGIC_VECTOR(11 DOWNTO 0);--正弦波数据表地址

BEGIN

da_mode<='0'; --DA选择二进制数据模式.

da_clk<=NOT clock;

PROCESS(clock) --同步锁存频率字、相位字

BEGIN

IF RISING_EDGE(clock) THEN

fword_r<=fword;

pword_r<=pword;

END IF;

END PROCESS;

PROCESS(clock) --频率相位累加器

BEGIN

IF RISING_EDGE(clock) THEN

freq_count<=freq_count + fword_r;

END IF;

END PROCESS;

PROCESS(clock) --相位调制器

BEGIN

IF RISING_EDGE(clock) THEN

rom_addr<=freq_count(31 DOWNTO 20) + pword_r;

END IF;

END PROCESS;

U1: dds_rom PORT MAP(address=>rom_addr,clock=>clock,q=>da_data);

END;

附录3DDS接口测试模块程序代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY dds_test IS

PORT(

clock: IN STD_LOGIC;--系统时钟48MHz

key: IN STD_LOGIC_VECTOR(7 DOWNTO 0);--按键输入key1 ~key8

fword: OUT STD_LOGIC_VECTOR(31 DOWNTO 0);--要发送的数据。

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管段码输出。

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管位码输出。

);

END;

ARCHITECTURE one OF dds_test IS

SIGNAL fword_r: STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL seg_r: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL dig_r: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL count: STD_LOGIC_VECTOR(16 DOWNTO 0);--时钟频计数器

SIGNAL dout1,dout2,dout3: STD_LOGIC_VECTOR(7 DOWNTO 0);--消抖寄存器

SIGNAL buff: STD_LOGIC_VECTOR(7 DOWNTO 0);--边沿检测寄存器

SIGNAL cnt: STD_LOGIC_VECTOR(2 DOWNTO 0);--数码管扫描计数器

SIGNAL disp_dat: STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管扫描显存

SIGNAL key_edge: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL div_clk: STD_LOGIC;--分频时钟

BEGIN

PROCESS(clock) --时钟分频部分

BEGIN

IF RISING_EDGE(clock) THEN

IF count<X"1D4C0" THEN--120000

count<=count+1;<, span style='font-family: "Times New Roman"; font-size: 12pt;'>

div_clk<='0';

ELSE

count<=B"0_0000_0000_0000_0000";

div_clk<='1';

END IF;

END IF;

END PROCESS;

----------------------------------<<按键消抖部分

PROCESS (clock)

BEGIN

IF RISING_EDGE(clock) THEN

IF div_clk='1' THEN

dout1<=key;

dout2<=dout1;

dout3<=dout2;

END IF;

END IF;

END PROCESS;

PROCESS (clock)--按键边沿检测部分

BEGIN

IF RISING_EDGE(clock) THEN

buff<=dout1 OR dout2 OR dout3;

END IF;

END PROCESS;

key_edge<=NOT (dout1 OR dout2 OR dout3) AND buff;

PROCESS(clock)--按键1

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(0)='1' THEN--下降沿检测

fword_r(31 DOWNTO 28)<=fword_r(31 DOWNTO 28) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键2

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(1)='1' THEN--下降沿检测

fword_r(27 DOWNTO 24)<=fword_r(27 DOWNTO 24) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键3

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(2)='1' THEN--下降沿检测

fword_r(23 DOWNTO 20)<=fword_r(23 DOWNTO 20) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键4

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(3)='1' THEN--下降沿检测

fword_r(19 DOWNTO 16)<=fword_r(19 DOWNTO 16) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键5

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(4)='1' THEN--下降沿检测

fword_r(15 DOWNTO 12)<=fword_r(15 DOWNTO 12) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键6

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(5)='1' THEN--下降沿检测

fword_r(11 DOWNTO 8)<=fword_r(11 DOWNTO 8) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键7

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(6)='1' THEN--下降沿检测

fword_r(7 DOWNTO 4)<=fword_r(7 DOWNTO 4) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)--按键8

BEGIN

IF RISING_EDGE(clock) THEN

IF key_edge(7)='1' THEN--下降沿检测

fword_r(3 DOWNTO 0)<=fword_r(3 DOWNTO 0) + 1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)

BEGIN

IF RISING_EDGE(clock) THEN

IF div_clk='1' THEN

cnt<=cnt+1;

END IF;

END IF;

END PROCESS;

PROCESS(clock)

BEGIN

IF RISING_EDGE(clock) THEN

IF div_clk='1' THEN

CASE(cnt) IS---------选择扫描显数据

WHEN "000"=>disp_dat<=fword_r(31 DOWNTO 28); --第一个数码管

WHEN "001"=>disp_dat<=fword_r(27 DOWNTO 24); --第二个数码管

WHEN "010"=>disp_dat<=fword_r(23 DOWNTO 20); --第三个数码管

WHEN "011"=>disp_dat<=fword_r(19 DOWNTO 16); --第四个数码管

WHEN "100"=>disp_dat<=fword_r(15 DOWNTO 12); --第五个数码管

WHEN "101"=>disp_dat<=fword_r(11 DOWNTO 8); --第六个数码管

WHEN "110"=>disp_dat<=fword_r(7 DOWNTO 4); --第七个数码管

WHEN "111"=>disp_dat<=fword_r(3 DOWNTO 0); --第八个数码管

END CASE;

CASE(cnt) IS

WHEN "000"=> dig_r<="01111111";--选择第一个数码管显示

WHEN "001"=> dig_r<="10111111";--选择第二个数码管显示

WHEN "010"=> dig_r<="11011111";--选择第三个数码管显示

WHEN "011"=> dig_r<="11101111";--选择第四个数码管显示

WHEN "100"=> dig_r<="11110111";--选择第五个数码管显示

WHEN "101"=> dig_r<="11111011";--选择第六个数码管显示

WHEN "110"=> dig_r<="11111101";--选择第七个数码管显示

WHEN "111"=> dig_r<="11111110";--选择第八个数码管显示

END CASE;

END IF;

END IF;

END PROCESS;

PROCESS(disp_dat) --七段译码

BEGIN

CASE disp_dat IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

WHEN OTHERS=> seg_r<=X"FF";

END CASE;

END PROCESS;

dig<=dig_r;

seg<=seg_r;

fword<=fword_r;

END;

附录4 FPGA设计总体RTL电路图

附录5 EP1C6Q240电路原理图 附录5 EP1C6Q240电路原理图

,

基于FPGA的DDS的设计

摘要:在电子技术飞速发展的今天,人们对于信号源的要求也逐渐提高。传统的信号源采用独立元件或简单数字电路设计,导致了经济代价大,设计周期长,产品的升级换代困难等诸多不足,显然已经不适合现代电子技术的要求。因此,要利用全新的思路设计符合要求的信号源。采用DDS技术已成为当前设计信号源的主流方法,DDS是指直接数字式频率合成器,它是利用相位的概念直接合成用户所需波形,主要包括相位累加器,波形存储器,数模转换器和低通滤波器组成,通过FPGA利用硬件描述语言VHDL来进行此设计。与传统的信号源相比,利用DDS原理设计的信号源具有频率分辨率高,频率转换速度快,切换相位连续等优点,使用FPGA来进行设计,大大缩短了设计周期,降低了研发和制作成本,同时设计可以根据用户不同需求进行改进和升级。

关键字:信号源;DDS;FPGA

DDS Based on the design of the FPGA

Student majoring in Electronic information science and technology Liu tong

Tutor Sun hong yan

Abstract:In the electronic technology rapid development today, people for the signal source requirement also gradually improve. The traditional signal source adopt independent components or simple digital circuit design, leading to the economic cost, the design cycle is long, the upgrade of products such as difficulty some shortcomings, have apparently not suitable for the modern electronic technology requirements. Therefore, to take advantage of the new idea design to meet the requirements of source. The technology has become the DDS design method of the mainstream of the signal source, is referred to as a direct DDS digital frequency synthesizer, it is to use the concept of phase the direct synthesis of customer need waveforms, mainly including phase accumulators, waveform memory, digital-to-analog converters and low pass filter composition, through the FPGA use hardware description language to this design VHDL. Compared with the traditional signal source, using the principle of the signal source has design DDS frequency resolution is high, the frequency conversion speed, switch phase continuous etc, and use to design the FPGA, greatly reducing the design period, lower the cost of making the research and development, and, at the same time, according to the different needs of the users design can improve and upgrades.

Key words:signal source;signal source;DDS;FPGA

1 绪论

1.1 设计背景

我国的电子行业伴随着经济的飞速增长进入了本行业发展的春天,随着物质生活的不断丰富,人们对于电子产品的要求不仅体现在需求量上,而且还表现在对产品的功能上。正因为如此,我国的电子市场正在迅速扩大,有着十分广阔的市场前景。

数字电子技术的飞速发展,有力地推动和促进了信息化的提高,它的应用已经渗透到我们生活的各个方面。不管是从计算机到手机,还是数字电话到数字电视,甚至军用设备、工业自动化及航天技术,都是采用了数字电子技术,它的核心是EDA(电子设计自动化,Electronic Design Automation)技术。就是以计算机工作平台,以EDA软件工具为开发环境,以硬件描述语言为设计语言,以可编程器件为实验载体,以电子系统设计为应用方向的电子产品自动化设计过程。它是以计算机科学和微电子技术发展为先导的,汇集了计算机图形学、拓扑逻辑学、微电子工艺与结构学和计算数学等多种计算机应用学科的最新成果的先进技术,是在先进计算机工作平台上开发出来的一整套电子系统设计的软件工具。

FPGA(现场可编程器件,Field Programmable Gate Array)便是EDA技术的一个分支,是20世纪80年代中期出现的高密度可编程器件,短短几十年来,取得了惊人的发展,其单片集成密度从最初的1200门发展到目前的几百万门,而且时钟频率由最初的不到10MHz发展到目前的300MHz,FPGA的结构类似于掩膜可编程门阵列(MPGA),有许多独立的可编程模块组成,用户可以通过编程将这些模块连接起来实现不同的设计。高密度可编程器件可以通过硬件描述语言进行设计,使得硬件的修改像软件一样方便,这一特性使得产品的研发时间大大缩短,便于产品的升级换代。高密度可编程可以设计成任何数字器件,无论是简单的门电路,还是高性能的处理器,它的发明对于数字电子电子技术来说具有里程碑式的意义。

通信是FPGA的传统领域。随着未细化的进步,芯片的面积越来越小、价格越来越低,市场发展正在逐步加快,同时由于FPGA灵活方便,不仅性能、速度、连接具有优势,而且可以缩短上市时间,因此应用领域在不断扩展。现在,许多用户都开始在一些批量生产的消费类电子产品上采用FPGA,如DVD、TV、游戏设备、空调、PDA、数字视频移动网络、无线局域网等。

1.2 设计的意义

在电子产品的研发,检测和维修等环节,都会用到信号源,而随着电子产品的品质不断提高,传统的信号源已经不能满足现代电子技术在其频率分辨率、转换速度等方面的要求;而有时我们需要通过计算机来控制信号源,从而完成一些复杂的操作。随着数字信号处理和集成电路技术的发展,DDS(直接数字频率合成器)得到越来越广泛的应用,DDS有如下优点:频率分辨率高,输出频点多,可达2的n次方个频点(n为相位累加器位数);频率切换速度快,可达us量级;频率切换时相位连续;可以输出宽带正交信号;输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻。

现代电子行业正在朝着功能更强,功耗更低,体积更小,速度更快,精度更高的方向发展,这些要求推动着集成电路不断发展。现场可编程器件(FPGA)具有集成度高,逻辑实现能力强、设计灵活性好等优点,可以快速完成复杂的数字系统的设计,符合现代电子行业的发展趋势,因此FPGA具有更强大的功能和市场前景,受到电子设计工程师们的普遍欢迎。

传统的信号源采用独立元件设计,导致体积庞大,不易携带,且功耗很高,这些缺点大大限制了它们的使用范围和效能,此设计利用FPGA为载体,不仅克服了上述不足,减小了体积,降低了功耗,而且设计的信号源性能更加优良,性能的提高不仅在研发过程中可以提高产品的质量,而且在检修过程中可以大幅度提高工作效率,发现一些不易发现的故障。而设计还可以根据需要进行升级和功能的扩展,表现出了极强的市场生命力。

1.3 设计实现的目标

本设计利用FPGA和外围电路来进行对DDS信号源的设计,并且利用EDA开发软件QuartusⅡ来进行设计和功能仿真,设计的性能要求:

(1)能够输出典型的正弦波。

(2)通过键盘控制频率的大小,并且利用数码管显示出来。

(3)输出的峰峰值≤5V.

2设计方案

2.1 DDS设计

2.1.1 DDS设计原理

频率合成技术是将一个(或多个)基准频率变换成另一个(或多个)合乎质量要求的所需频率的技术。

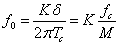

一个的简单的原始单频信号可表示为:

(2-1) (2-1)

在它的初始相位θ0和幅度U不变的情况下,它的频谱为一条谱线,频率为f0。在这里,为了简化表示,令U=1,θ0=0,这是不会影响系统研究的,简化后的信号可以表示为:

(2-2) (2-2)

如果对(2-2)式中表示的信号进行采样,令采样周期为Tc(即采样频率为fc),则可得到离散的波形序列:

(2-3) (2-3)

相应的离散相位序列为:

(2-4) (2-4)

式中:

(2-5) (2-5)

是连续两次采样之间的相位增量。根据采样定理:

(2-6) (2-6)

分析上述关系式得:只要(2-3)式中的离散序列确定,便可唯一的恢复出(2-2)式中的模拟信号。从(2-2)可知,是相位函数的斜率决定了信号的频率;从(2-5)可知,决定相位函数斜率的是两次采样之间的相位增量Δθ。因此,只要控制这个相位增量,就可以控制合成信号的频率。现将整个周期的相位2 分成M份,每一份为δ=2π/M,若每次的相位增量选择为δ的K倍,即可得到信号的频率: 分成M份,每一份为δ=2π/M,若每次的相位增量选择为δ的K倍,即可得到信号的频率:

(2-7) (2-7)

相应的模拟信号为:

(2-8) (2-8)

式中K和M都是正整数,根据采样定理的要求,K的最大值应小于M的1/2。

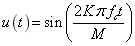

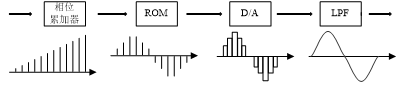

综上所述,在采样频率一定的情况下,可以通过控制两次采样之间的相位增量(不得大于π)来控制所得离散序列的频率,经保持、滤波之后可唯一的恢复出此频率的模拟信号。DDS设计原理图如图2-1所示:

图2-1 DDS设计原理图

主要构成:

内部:相位累加器,波形存储器

外围:D/A转换器,LPF(低通滤波器)

图中M为频率控制字,N为相位累加器的位数,D为相位累加器的输出位数,A为波形存储部分输出的幅度码的位数,参考频率源的频率为fclk,输出频率为fout.。

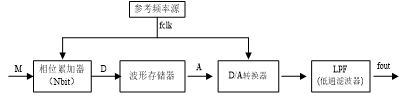

2.1.2 DDS工作过程

在每一个参考频率fclk作用下,加法器就将频率控制字M与累加寄存器输出的累加相位数据相加,相加的结果又反馈到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率字相加。这样相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位采样地址,这样就可以把存储在波形存储器内的波形采样值(二进制编码)经查表找出,完成相位到幅值的转换。波形存储器的输出送到D/A转换器,由D/A转化器将数字信号转换成模拟的阶梯电压信号,阶梯电压信号经过低通滤波器平滑后,可以得到所需的正弦波信号。DDS信号流程示意图如图2-2所示:

图2-2 DDS信号流程示意图

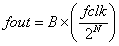

由于相位累加器为N位,相当于把正弦信号在相位上的精度定为N位(N的取值范围一般为24~32),所以其分辨率为1/ 2N。若系统的时钟频率为fclk,频率控制字M为1,则输出频率为:fout=fclk/2N,这个频率相当于“基频”。若M为B则输出频率为:

(2-9) (2-9)

当系统输入时钟fclk不变时,输出信号频率由M所决定。由上式可得:

(2-10) (2-10)

其中B为频率控制字,注意B要取整。

2.2 FPGA设计DDS的原理

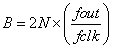

根据DDS的实现原理,使用FPGA设计DDS更为实用,足够大的逻辑单元,保证了可以实现很小的步进频率,提高产品的精度,且辅助有高速的D/A转换器可以做到很高的频率。FPGA设计DDS原理框图如图2-3所示:

图2-3 DDS原理框图

在主输入时钟fclk和步进累加器步进值M的共同作用下,累加器输出波形数据表地址,在ROM中查得相应波形当前幅度值,从而确定输出波形。

2.3 FPGA器件的选择与简介

FPGA是现场可编程门阵列(Field Programmable Gate Array)的英语缩写,它是在阵列的各个节点放上由门 、触发器等做成的逻辑单元,并在各个单元之间预先制作了许多连线。在FPGA中常用的编程工艺有反熔丝和SRAM两类。综合考虑设计、仿真和调试的全过程,在此主要考虑选用Altera公司的Cyclone系列的FPGA芯片。

Cyclone是Altera公司2003年推出的产品系列,它集合了可编程器件的灵活性,采用0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列 ,是目前主流产品,其配置芯片也改用全新的产品。系统时钟可以达到275MHZ,兼容66MHZ,64 bit PIC,采用独特的嵌入式阵列和逻辑阵列的逻辑实现结构,同一系列相同封装的芯片在管脚上满足兼容。

同时,可为用户提供92Kbit的片内RAM,其双口RAM为独立的读写操作提供了独立的读、写端口,且每个I/O口都有寄存器;PLL时钟管理和时钟增强电路提高了系统的性能,并且可以提供时钟倍频;专用进位链路,可实现快速加法器和计数器功能;专用级联链路,支持系统集成;支持多时钟系统的低时滞要求;具有JTAG边界扫描测试内速电路。本设计中采用Altera公司的Cyclone系列芯片EP1C6Q240,作为实现DDS的FPGA芯片。EP1C6Q240的主要参数如表2-4所示:

|

逻辑单元(LE)

|

4K bit+奇偶校验 4K bit+奇偶校验

|

I/O门数

|

RAM总量 /bit

|

PLL

|

配置二进制文件大小(bit)

|

可选串行主动配置器件

|

|

5980

|

20

|

185

|

92160

|

2

|

1167216

|

EPCS1/EPCS4/EPCS16

|

表2-4 EP1C6Q240的主要参数

其3.3V外部电源和TTL、CMOS电平兼,丰富的寄存器资源和I/O口,48MHZ的工作频率满足基准时钟10MHZ的要求,其优良的特性完全可以实现DDS芯片的功能。电路原理图见附录5。

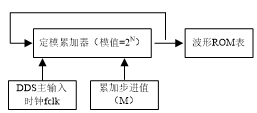

2.4 开发环境简介

本设计利用Altera公司提供的开发FPGA的集成环境QuartusⅡ,简单易学易用,其可视化、集成化设计环境等优点为大家公认,从设计输入、仿真、编译、综合、布局布线和下载都可以使用这个集成环境来完成。它提供了一种与结构无关的设计环境,我们只需要使用自己熟悉的开发工具,通过软件提供的各种输入方式进行编译、仿真和综合,便可设计出需要的可编程器件。QuartusⅡ能够直接满足特定的设计需要,为可编程器件提供全面的设计环境,它含有FPGA设计所有阶段的解决方案,其设计流程图如2-5所示

图2-5 FPGA设计流程图

此外,QuartusⅡ软件为设计流程的每个阶段提供QuartusⅡ图形用户界面、EDA工具界面和命令行界面。可以在整个流程中只是用这些界面中的一个,也可以在设计流程的不同阶段使用不同的界面。

2.5 设计语言选择与简介

全套毕业设计论文现成成品资料请咨询微信号:biyezuopinvvp QQ:1015083682

返回首页

如转载请注明来源于www.biyezuopin.vip

|