3.3 模型机流水硬连线控制器设计

3.3.1 模型机流水硬连线控制器设计

一、教学目的

⑴ 融会贯通计算机组成与体系结构课程各章教学内容,通过知识的综合运用,加深对

CPU 各模块工作原理及相互联系的认识。

⑵ 掌握流水硬连线控制器的设计方法。

⑶ 学习运用当代的 EDA 设计工具,掌握用 EDA 设计大规模复杂逻辑电路的方法。

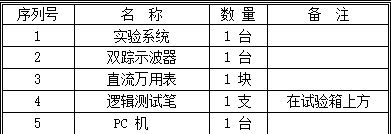

⑷ 培养科学研究能力,取得设计和调试的实践经验。二、实验设备

⑷ 培养科学研究能力,取得设计和调试的实践经验。二、实验设备

三、设计与调试任务

1.设计一个流水硬连线控制器,和 TEC-8 模型计算机的数据通路结合在一起,构成一个完整的 CPU,该 CPU 要求:

⑴ 能够完成控制台操作:启动程序运行、读存储器、写存储器、读寄存器和写寄存器。

⑵ 能够执行本章第 3.1 节的表 3.1 中的指令,完成规定的指令功能。2.在 Quartus Ⅱ下对硬连线控制器对设计方案进行编程和编译

3. 将编译后的流水硬连线控制器下载到 TEC-8 实验台上的 ISP 器件 EPM7128 中去,使EPM7128 成为一个流水硬连线控制器。

4.根据指令系统,编写检测流水硬连线控制器正确性的测试程序,并用测试程序对硬连线控制器在单拍方式下进行调试,直到成功。

5.在调试成功的基础上,整理出设计文件,包括:

⑴ 流水硬连线控制器逻辑模块图

⑵ 流水硬连线控制器指令周期流程图

⑶ 流水硬连线控制器的 VHDL 源程序

⑷ 测试程序

⑸ 设计说明书

⑹ 调试总结

四、设计提示

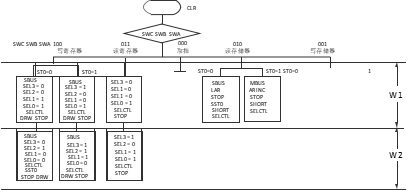

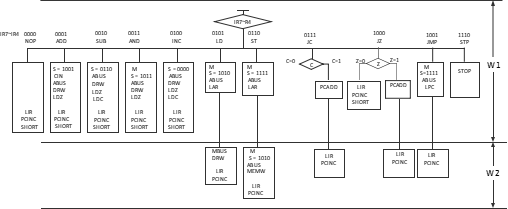

1.流水硬连线控制器参考流程图

流水硬连线控制器参考流程图见图 3.3。

|

|

|

ST0=

|

|

SBUS

|

|

SBUS

|

|

LAR

|

MEMW

|

|

STOP

|

ARINC

|

|

SST0

|

STOP

|

|

SHORT

SELCTL

|

SHORT SELCTL

|

图 3.3 流水硬连线控制器参考流程图

图 3.3 流水硬连线控制器参考流程图

在 TEC-8 实验系统中,由于按下复位按钮 CLR 后,指令寄存器 IR 被复位为 00H,因此, 无论存储器中写入什么测试程序,在图 3.3 所示的流程图中,第 1 条被执行的指令的代码总是 00H。我们规定,指令代码为 00H 的指令是条 nop 指令。

其它的设计提示参考本章 3.1 节。

五、设计报告要求

1. 采用 VHDL 语言描述流水硬连线控制器的设计,列出设计源程序。

2. 测试程序。

3. 写出调试中出现的问题、解决办法、验收结果。

4. 写出设计、调试中遇到的困难和心得体会。

3.3.2 实验报告记录:

3.4 含有阵列乘法器的 ALU 设计

3.4.1 含有阵列乘法器的 ALU 设计

一、教学目的

⑴ 掌握阵列乘法器的组织结构和实现方法。

⑵ 改进 74181 的内部结构设计,仅实现加、减、乘、传送、与、加 1、取反、求补等 8 种操作。

⑶ 学习运用当代的 EDA 设计工具,掌握用 EDA 设计大规模复杂逻辑电路的方法。

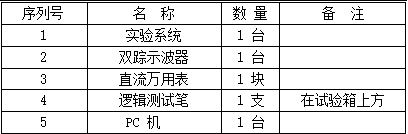

⑷ 培养科学研究能力,取得设计和调试的实践经验。二、实验设备

⑷ 培养科学研究能力,取得设计和调试的实践经验。二、实验设备

三、设计与调试任务

1.设计 1 个 4 位×4 位的阵列乘法器,其积为 8 位。

2.设计一个 ALU,能够对 2 个 4 位操作数 A 和 B 进行 8 种运算,由 3 位操作码控制进行何种运算。3 位操作码从电平开关 SWA、SWB、SWC 输入。要求:

|

操作模式

|

功能选择

|

备 注

|

|

000

|

A+B

|

|

|

001

|

A-B

|

|

|

010

|

A and B

|

|

|

011

|

A or B

|

|

|

100

|

not A

|

|

|

101

|

A xor B

|

|

|

110

|

not(A and B)

|

|

|

111

|

乘

|

|

|

|

|

|

操作数 A 从开关 K3~K0 输入,操作数 B 从开关 K11~K8 输入。运算结果送指示灯 L7~L0 输出,L0 为最低位,L7 为最高位。在做加、减法时,L4 显示进位。在做与、或、求反、异或、与非运算时,L7~L4 显示 0。

2.在 Quartus Ⅱ下对改进 ALU 的设计方案进行编程和编译

3.将编译后的 ALU 下载到 TEC-8 实验台上的 ISP 器件 EPM7128 中去,使 EPM7128 成为含有阵列乘法器的 ALU。

4.测试方法和正确性验证。

5.写出设计、调试报告总结。

四、设计提示

1.无符号阵列乘法器结构

无符号阵列乘法器的结构框图如图 3.4 所示。它由一系列全加器 FA 用流水方法(时间并行)和资源重复方式(空间并行)有序组成。图 3.4 所示为 5×5 位的阵列乘法器。

P9 P8

P7 P6

P5 P4 P3

P2 P1 P0

图 3.4 无符号阵列乘法器框图

2.EPM7128 和电平开关 K15~K0、指示灯 L11~L0 的连接

EPM7128 通过一条 34 芯扁平电缆和电平开关 K15~K0、指示灯 L15~L0 连接。连接时扁平电缆的 34 芯端插到插座 J6 上,扁平电缆的 12 芯端插到插座 J4 上(请注意:P12 的滑面朝下或者箭头朝在左边),16 芯插到插座 J8 上。电平开关 K15~K0、指示灯 L11~L0 对应的

EPM7128 引脚如下表 3.5 所示。

表 3.5 电平开关、指示灯对应的 EPM7128 引脚号

|

电平开关

|

方向

|

引脚号

|

指示灯

|

方向

|

引脚号

|

|

S0

|

输入

|

54

|

L0

|

输出

|

37

|

|

S1

|

输入

|

81

|

L1

|

输出

|

39

|

|

S2

|

输入

|

80

|

L2

|

输出

|

40

|

|

S3

|

输入

|

79

|

L3

|

输出

|

41

|

|

S4

|

输入

|

77

|

L4

|

输出

|

44

|

|

S5

|

输入

|

76

|

L5

|

输出

|

45

|

|

S6

|

输入

|

75

|

L6

|

输出

|

46

|

|

S7

|

输入

|

74

|

L7

|

输出

|

48

|

|

S8

|

输入

|

73

|

L8

|

输出

|

49

|

|

S9

|

输入

|

70

|

L9

|

输出

|

50

|

|

S10

|

输入

|

69

|

L10

|

输出

|

51

|

|

S11

|

输入

|

68

|

L11

|

输出

|

52

|

|

S12

|

输入

|

67

|

|

|

|

|

S13

|

输入

|

65

|

|

|

|

|

S14

|

输入

|

64

|

|

|

|

|

S15

|

输入

|

63

|

|

|

|

|

SWA

|

输入

|

4

|

|

|

|

|

SWB

|

输入

|

5

|

|

|

|

|

SWC

|

输入

|

6

|

|

|

|

3.运算测试

⑴ 用测试数据表 3.6 中的数据对乘法进行验证测试,运算结果正确。

表 3.6 乘法测试数据

|

组号数据

|

1

|

2

|

3

|

4

|

5

|

6

|

|

被乘数 A

|

9

|

15

|

0

|

15

|

随机

|

随机

|

|

乘数 B

|

8

|

15

|

15

|

0

|

随机

|

随机

|

|

乘积 P

|

72

|

225

|

0

|

0

|

|

|

⑵ ALU 的其它 7 种操作验证测试与乘法类似,自行设计测试数据表。五、设计报告要求

1. 采用 VHDL 语言或者原理图描述改进 ALU 的设计,列出源程序或者画出原理图。

2. 测试数据表及测试结果。

3. 写出调试中出现的问题、解决办法、验收结果。

4. 写出设计、调试中遇到的困难和心得体会。

六、实验完成后,必须要将硬连线控制器重新装入 EPM7128 中。以备以后做其他实验使用。

3.3.2 实验报告记录: