第 5 章:Quartus II 软件简易使用

5.1 软件安装:

安装 Quartus II 软件,步骤如下:

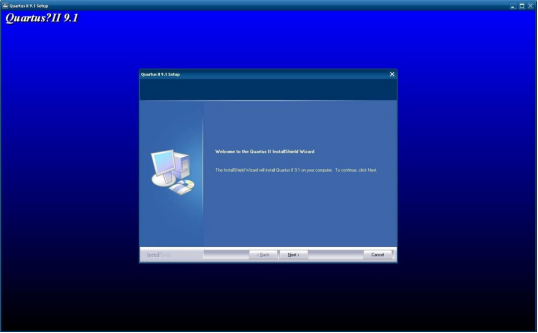

第一步:打开试验箱所带光盘,双击 Quartus II 文件夹目录下 Setup,单击 Next 按钮;

图 6.1

第二步:选择 I accept the terms of this license… 选项,并单击 Next 按钮;

图 6.2

第三步:填写用户名和公司名称后,点击 Next 按钮;

图 6.3

第四步:默认路径为:C:\altera\91,单击 Next 按钮;

图 6.4

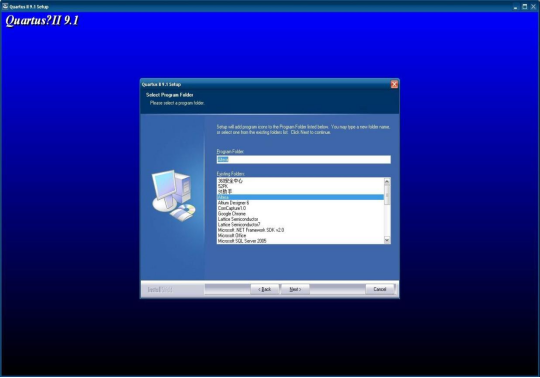

第五步:点击 Next 按钮;

图 6.5

第六步:点击 Next 按钮;连续几次;点击 Finish 按钮,完成安装。

图 6.6

5.2 实验步骤

1)使用 Quartus II 建立工程

Quartus II 是以工程(project)的方式对设计过程进行管理的,Quartus II 工程中存放创建 FPGA 配置文件所需要的所有设置和设计文件。因此,每个开发过程开始时都应建立一个 Quartus II 工程。

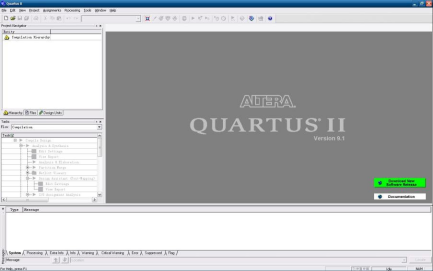

(1)选择“开始” -> “程序” -> Altera -> Quartus II 9.1 或单击桌面快捷方式打开Quartus II 软件,软件界面如图 6.7 所示。

图 6.7 Quartus 软件图形用户界面

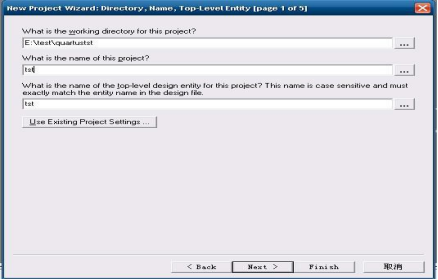

(2)在图 6.7 中选择 File -> New Project Wizard 新建一项工程。新建工程向导对话框如图 6.8

所示。在该对话框中需要设置:

①工程文件夹保存目录。

②工程名称。

③工程顶层文件设计实体名称。

图 6.8 新建文本输入对话框

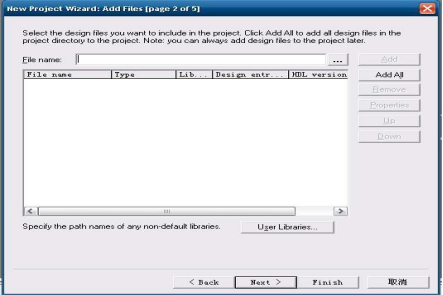

(3)单击 NEXT 进入图 6.9 所示对话框,由于是新建工程,暂无输入文件,直接单击 NEXT。

图 6.9【New project wizard】对话框

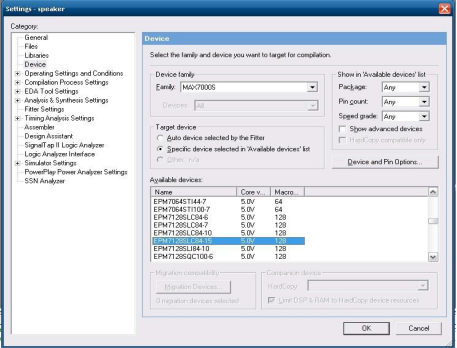

(4)弹出图 6.10 所示选择器件对话框。这里我们选择 TEC-8 核心板上所用的 Cyclone 系列的EPM7128SLC84-15.

图 6.10 【Settings】对话框

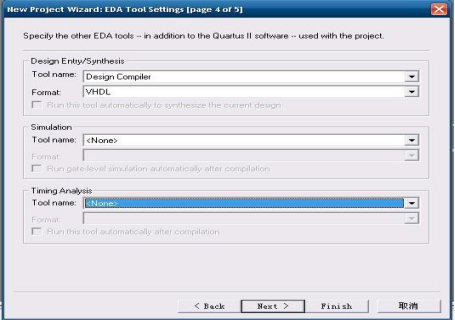

(5)指定完器件后,单击 NEXT,进入图 9 所示对话框,本实验利用 Quartus II 集成开发环境进行开发,不使用任何第三方 EDA 工具,因此这里不作任何改动。

图 6.11

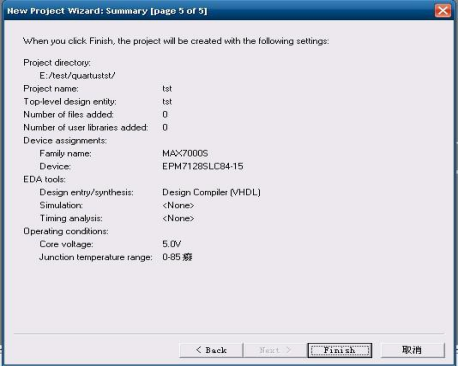

(6)在图 6.11 中单击 NEXT,设计者可以看到工程文件的配置信息报告。单击 FINISH 完成新工程的建立。

图 6.12

2)使用 Quartus II 建立设计文件

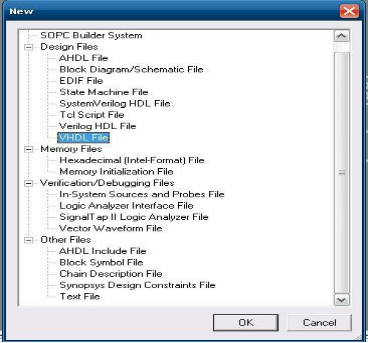

单击 FILE -> NEW,弹出图 6.13 所示对话框。在该对话框中选择输入文件类型,在本书所列试验中均选择 VHDL File。此时主界面中出现设计文件输入窗口。

图 6.13

在该窗口中输入设计文件如图 6.13 输入结束选择 FILE -> NEW 保存。

图 6.14

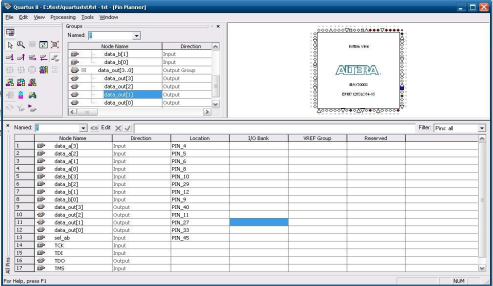

3)分配 FPGA 引脚

选择菜单 Assignments -> Pins 打开引脚分配对话框如图 13 所示。在 TO 栏中填入与设计文件中输入输出端口名称相对应的各引脚名称,在 Location 栏中选择相应的引脚,也可以在 Location 下直接输入引脚号来快速定位。(具体引脚号参考各实验说明)选择 FILE -> Save 来保存分配结果,然后关闭 Assignment Editor。

图 6.15 管脚分配对话框

4)编译整个工程

在编译过程中,编译器定位并处理所有工程文件,生成与编译相关的消息与报告,创建 SOF 文件及任何可选配置文件。

选择 Processing -> Start Compilation 进行全程编译。在编译过程中,状态窗口显示整个编译进程及每个编译阶段所用时间。编译结果显示在 Compilation Report 窗口中。编译结束后, 对话框显示消息“Full compilation was successful”,单击 OK 确定。

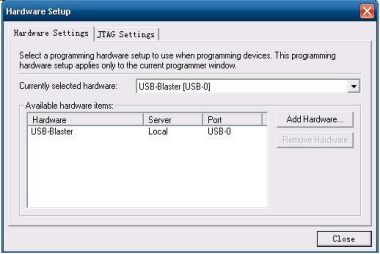

5)下载硬件设计到目标 FPGA 芯片(1)JTAG(下载后缀为 sof 的 FPGA 器件配置文件)

通过 ByteBlaster II 下载电缆连接试验箱 USB 口和计算机,接通试验箱电源。

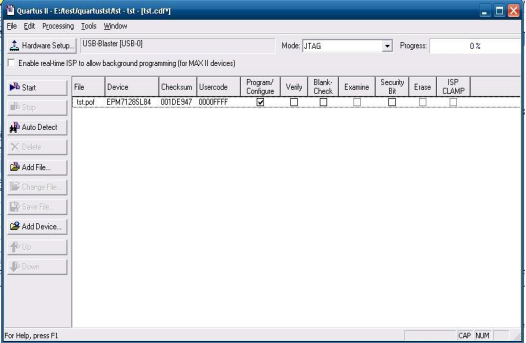

在 Quartus II 软件中选择 Tools->Programmer,打开编程器窗口,并自动打开配置文件

sof,如图 15 所示。单击 sof 文件的 Program configure 方框选中下载文件。

图 6.16

图 6.17

单击 Start 开始下载。进度条完成 100%则完成下载。