目录

1项目简介 4

1.1项目目标 4

1.2模块划分 4

1.3分工规划 5

1.4完成情况 5

2神经网络结构设计 5

2.1数据集选择 5

2.2网络结构 6

2.3超参数选择和模型训练 7

3各模块设计 7

3.1VGA 控制 7

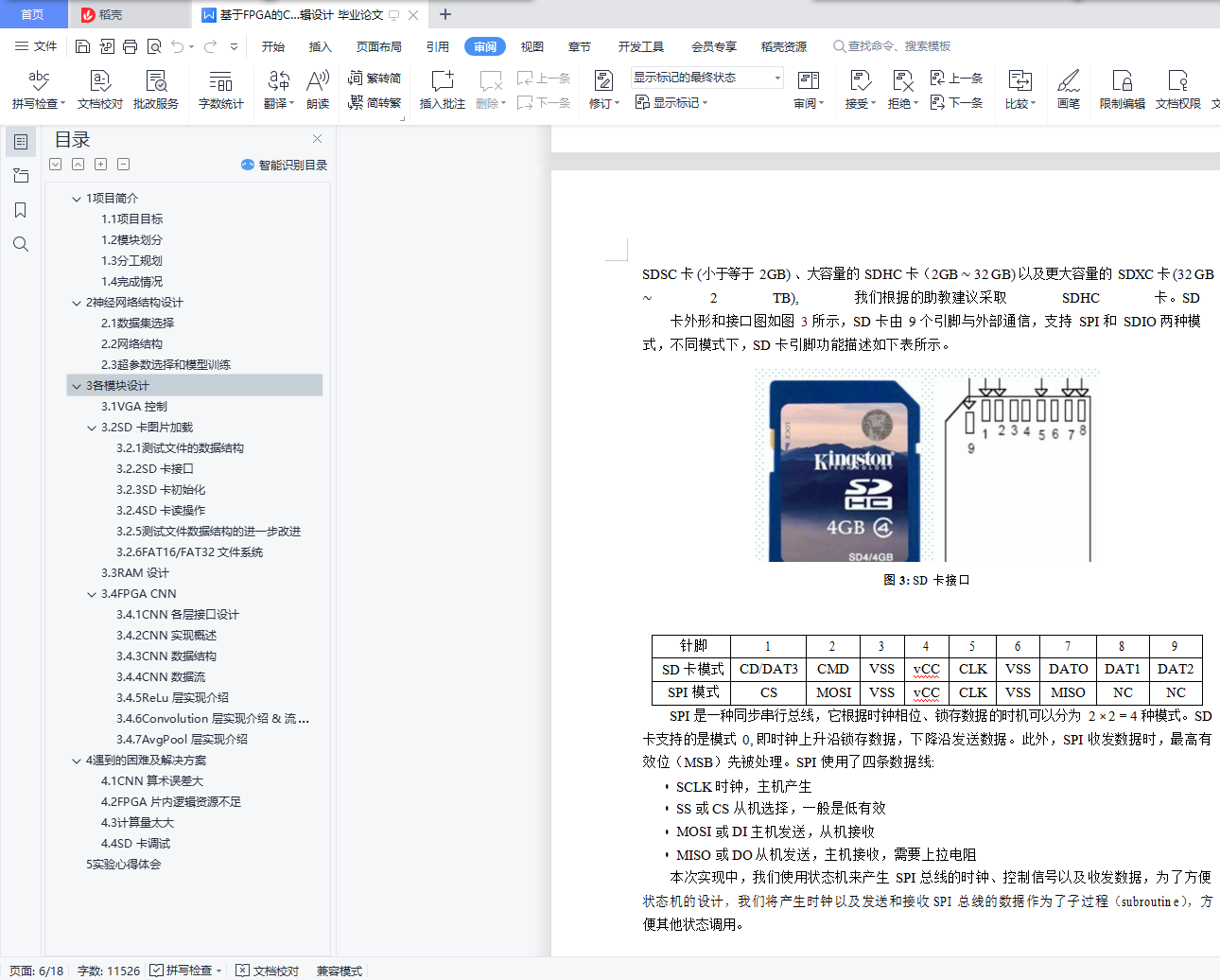

3.2SD 卡图片加载 7

3.2.1测试文件的数据结构 7

3.2.2SD 卡接口 7

3.2.3SD 卡初始化 8

3.2.4SD 卡读操作 9

3.2.5测试文件数据结构的进一步改进 10

3.2.6FAT16/FAT32 文件系统 10

3.3RAM 设计 13

3.4FPGA CNN 13

3.4.1CNN 各层接口设计 13

3.4.2CNN 实现概述 14

3.4.3CNN 数据结构 15

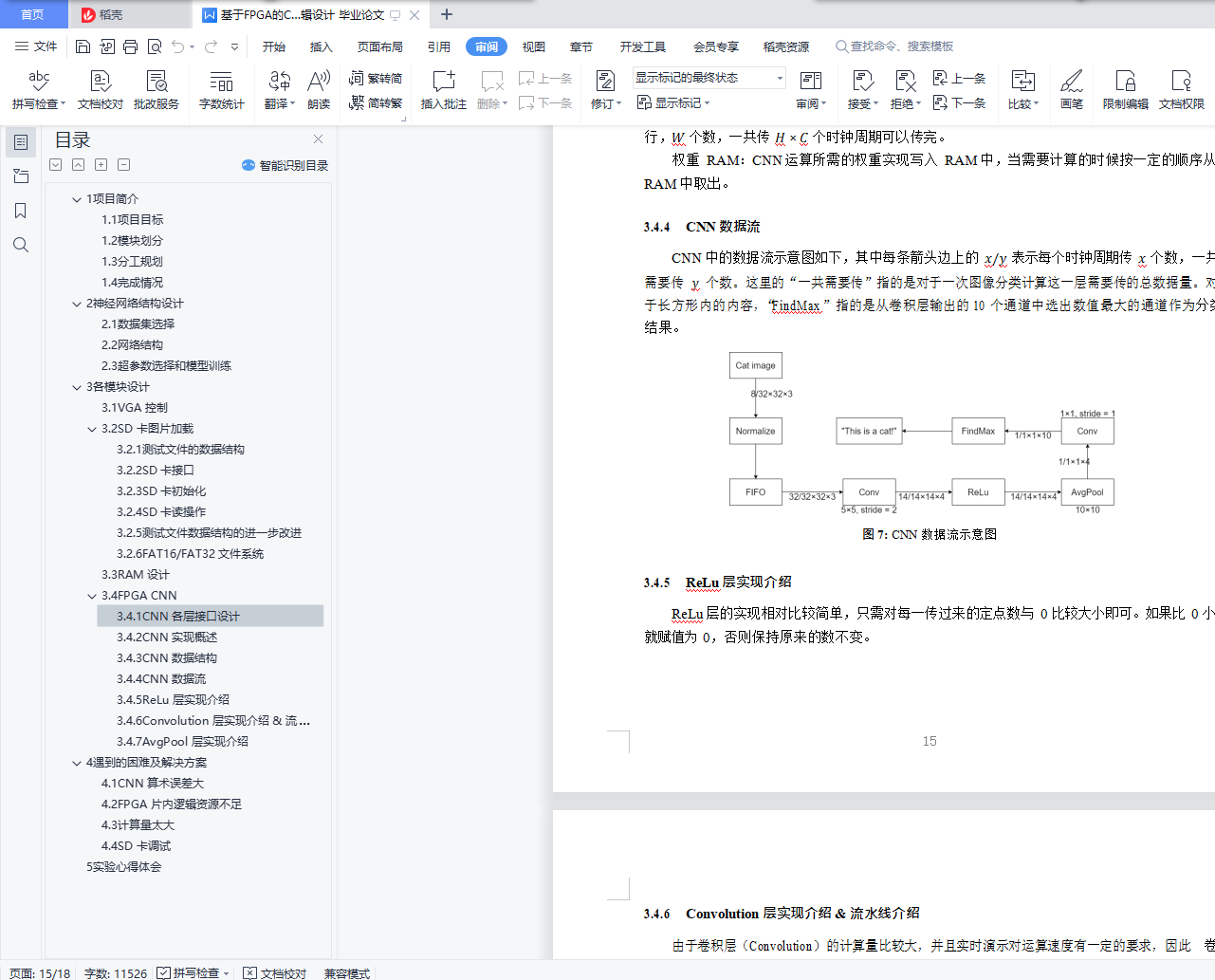

3.4.4CNN 数据流 15

3.4.5ReLu 层实现介绍 15

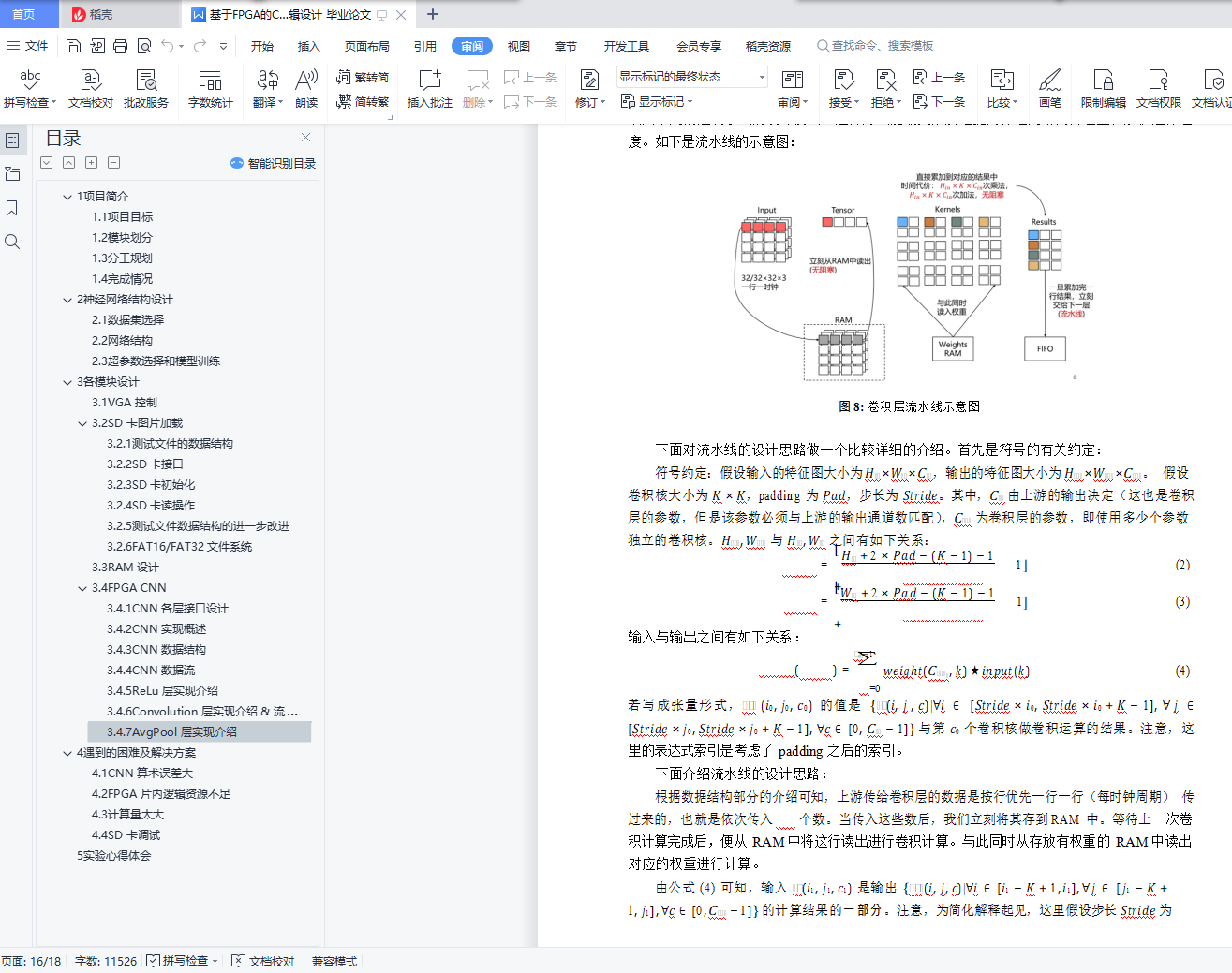

3.4.6Convolution 层实现介绍 & 流水线介绍 16

3.4.7AvgPool 层实现介绍 17

4遇到的困难及解决方案 17

4.1CNN 算术误差大 17

4.2FPGA 片内逻辑资源不足 17

4.3计算量太大 18

4.4SD 卡调试 18

5实验心得体会 18

1项目简介

1.1项目目标

近年来,人工智能开始显示出其在为人们的生活服务方面越来越大的潜力,但是,其庞大的计算需求使其很难在功能较弱的计算工具中实现。与 CPU 相比,FPGA 具有并行机制,因此速度更快。与 GPU 相比,FPGA 的功耗更低,消耗的能源更少。根据上述背景,我们最初的想法是在 FPGA 上实现卷积神经网络,利用 FPGA 的强大并行特性加速神经网络的计算,并将加速结果与基于 CPU 的神经网络进行对比。但跟助教、老师交流后,发现有两个明显的问题:1、FPGA 资源有限,即使有并行机制,其加速效果未必能比得上 CPU;2、单纯做硬件加速欠缺展示性。于是我们打算对选题进行调整。经过反复与助教的交流后,我们最终听从助教的建议,将“加速”改为“展示”,搭建一个基于 FPGA 的卷积神经网络,并将隐藏层结果输出到屏幕上进行展示。

一句话概括,我们希望基于 FPGA 实现卷积神经网络,并且利用神经网络搭建一个图像分类系统,为用户展示输入图像的分类结果以及神经网络隐藏层的计算中间结果。

1.2模块划分

我们要完成的事情主要有两件:一是将 CNN 实现在 FPGA 上,确保 CNN 的正确运行,二是将图片输入 FPGA,操控 CNN 完成分类并将结果输出到屏幕上。一种很自然的想法就是分别按照这两件事对模块进行划分。

神经网络我们单独作一个大模块来实现,分为输入层,隐藏层和输出层。神经网络的权重预先在电脑上训练好,转为二进制文件后通过 Quartus 写入片内。

图像输入通过 SD 卡实现。我们预先使用读卡器在 SD 卡写入图像,然后在将 SD 卡插入板上进行图像读写。图像的展示使用 VGA 实现。由于 VGA 渲染需要缓存,因此我们也在 RAM 为

VGA 预留了缓存。值得注意的是,由于我们选取的数据集(下面会详细介绍)的图像大小比较小,且神经网络的权重参数的大小也比较小,因此可以直接使用 RAM 当缓存使用。

本项目有两个重要的接口:输入图像与 CNN 之间的接口以及 CNN 输出与 VGA 之间的接口。对于前者,我们采用 FIFO + valid 的方法。一旦 SD 卡读出了图像,便将 valid 拉高,以流的形式将数据传入 CNN,CNN 用一个 FIFO 接收输出。对于后者,我们采用 Mux + valid 的方法, 一旦神经网络得到了稳定的结果,便将 valid 拉高,外界根据用户的指令选择对应的内容输入给

VGA 展示。值得注意的是,SD 卡、神经网络、VGA 的时序都是不同的,需要分别单独编写控制代码。