基于VHDL的简易CPU设计

目录

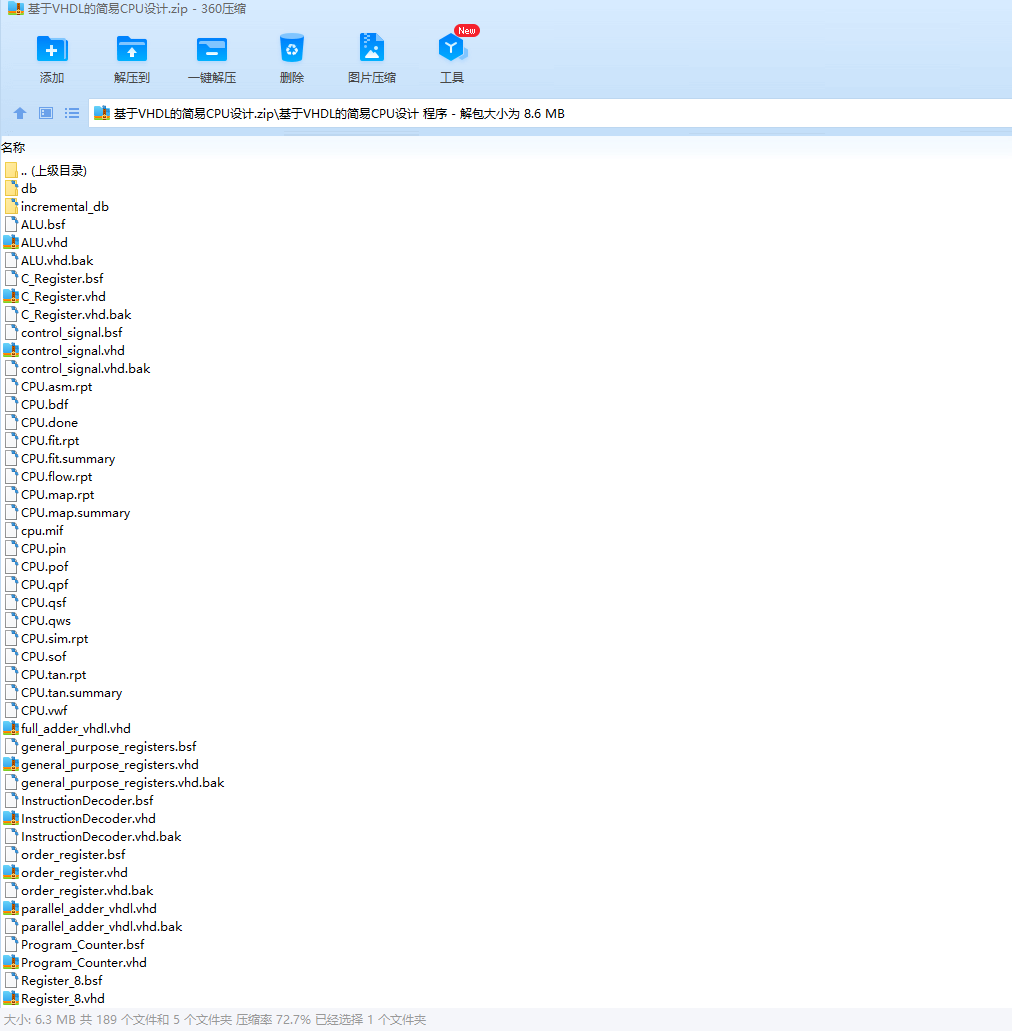

基于VHDL的简易CPU设计

一、设计目的

二、设计内容

三、 详细设计

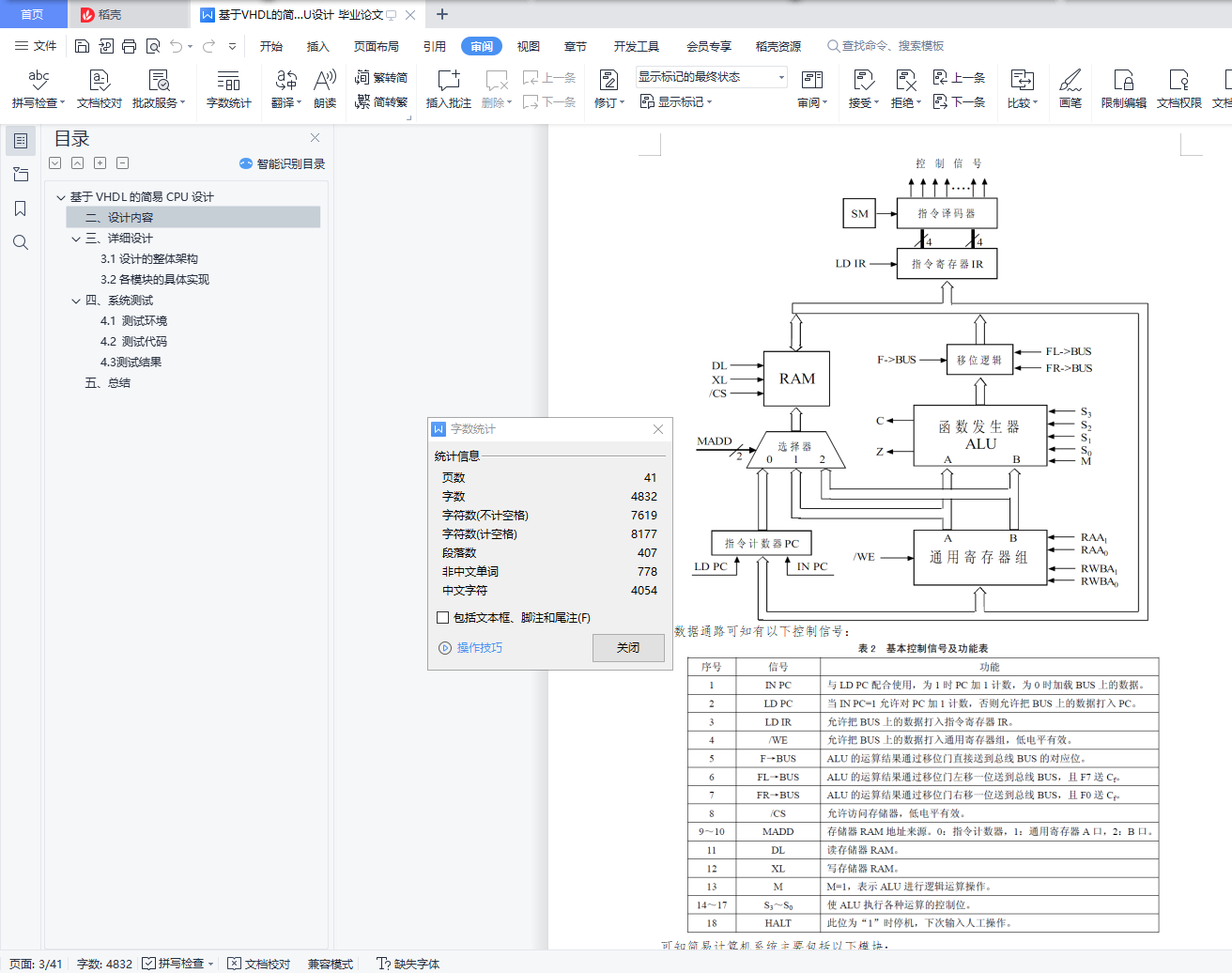

3.1设计的整体架构

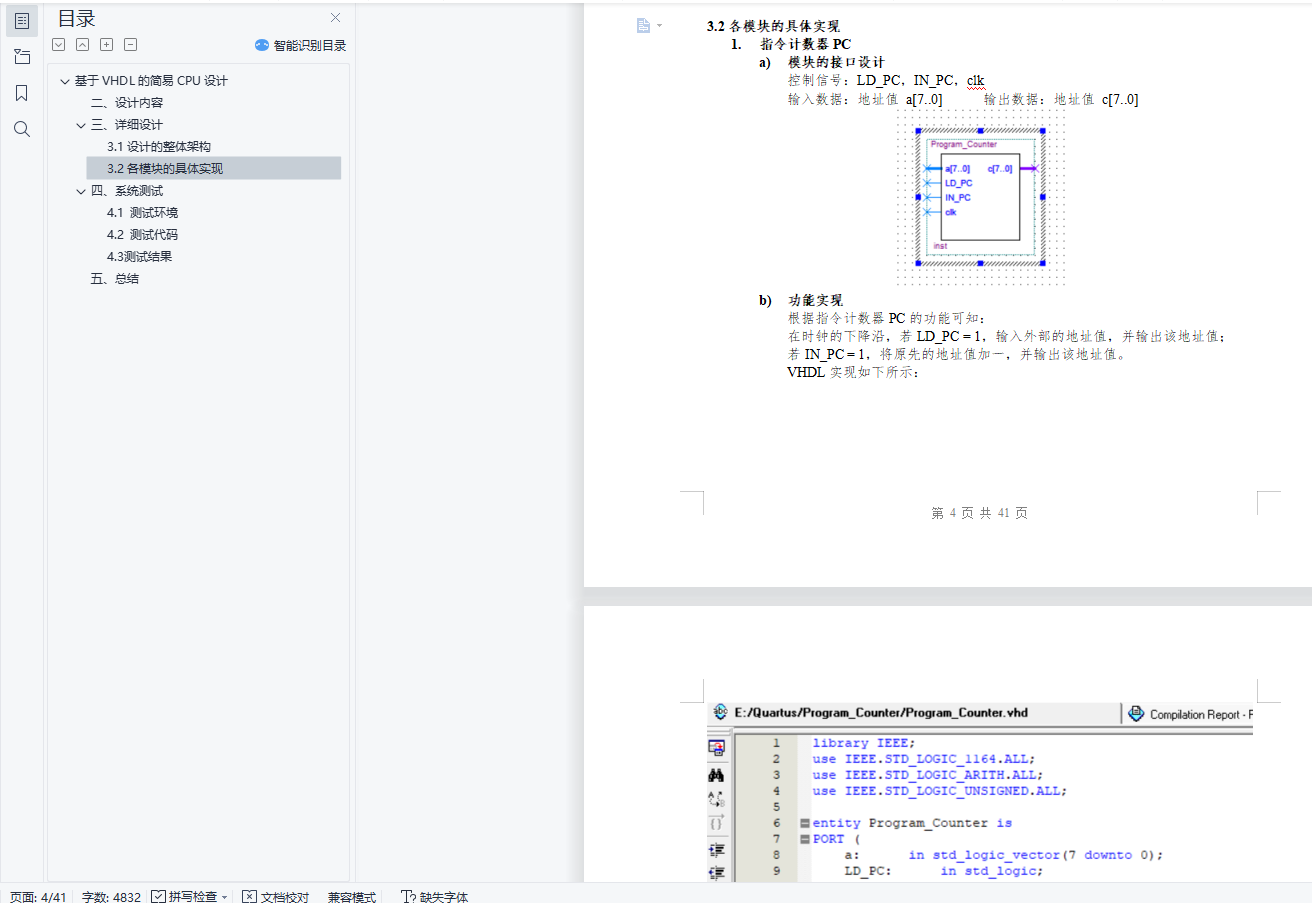

3.2各模块的具体实现

四、 系统测试

4.1 测试环境

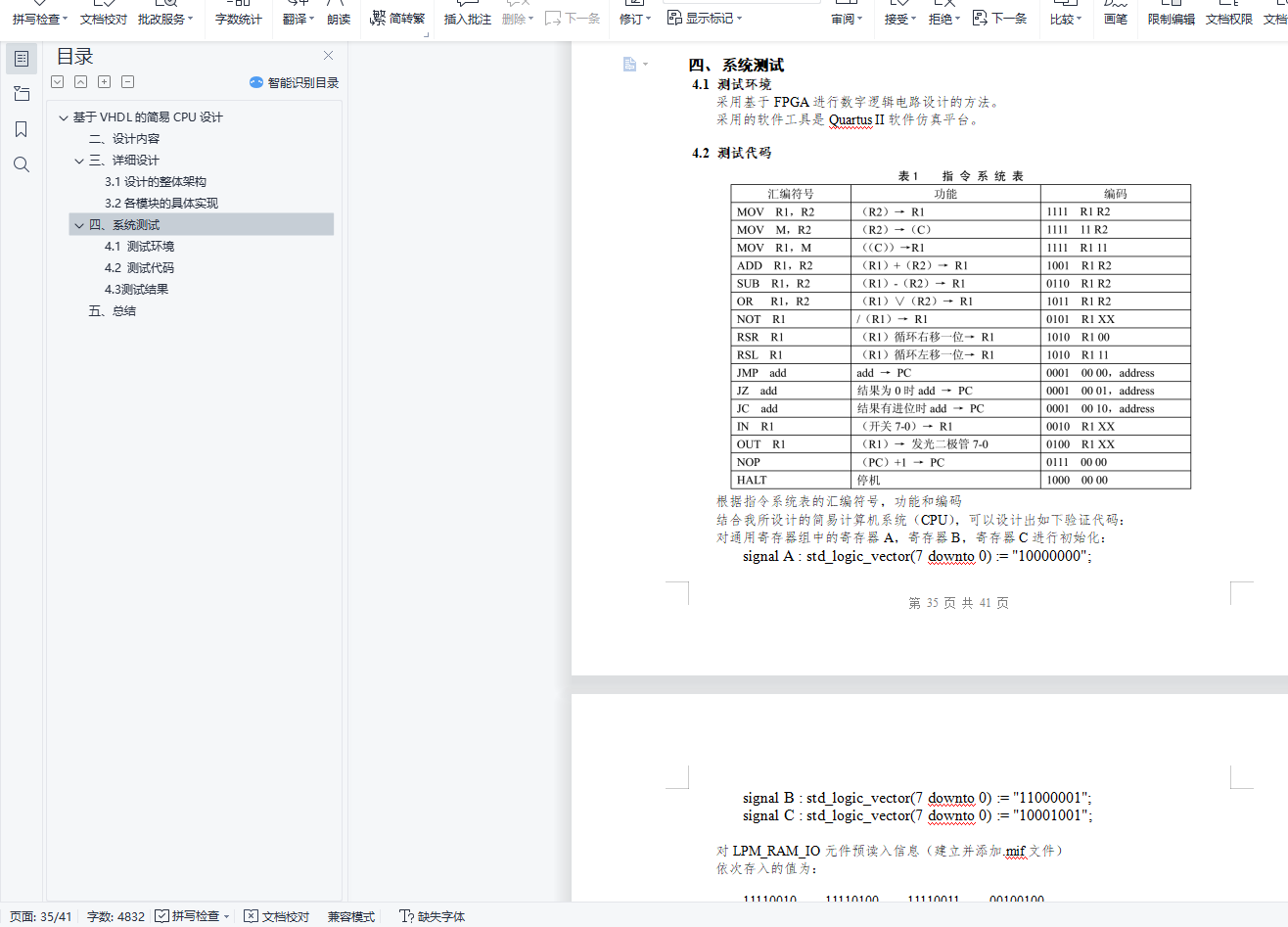

4.2 测试代码

4.3 测试结果

五、 总结

一、设计目的

1. 本课程力图以“培养学生现代数字系统设计能力”为目标,贯彻以CPU设计为核心,以层次化、模块化设计方法为抓手的组织思路,培养学生设计与实现数字系统的能力。

2. 本设计要求在进行了多个单元实验后,综合利用所学的理论知识,并结合在单元实验中所积累的成果(包括已经设计好的功能部件和调试方法),设计出一个简易计算机系统。

二、设计内容

1. 按给定的数据格式和指令系统,使用EDA工具设计一台用硬连线逻辑控制的简易计算机系统;

2. 要求灵活运用各方面知识,使得所设计的计算机系统具有较佳的性能;

3. 对所做设计的性能指标进行分析,整理出设计报告。

简易计算机系统

(一) 数据格式

数据字采用8位二进制定点补码表示,其中最高位(第7位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<1或-128≤X<127。

(二) 寻址方式

指令的高4位为操作码,低4位分别用2位表示目的寄存器和源寄存器的编号或表示寻址方式。