摘 要

随着网络的普及和发展,对数据的传输标准也在随之不断的提高。这就在数据的控制问题上提出了更大的要求。在数字信号中,数据一般都是以帧结构存在的,各个时隙的位置可以根据帧定界信号加以识别。因此在数字通信网中,帧同步是同步复接中最重要的部分,它包括帧同步码的产生和帧同步码的识别。

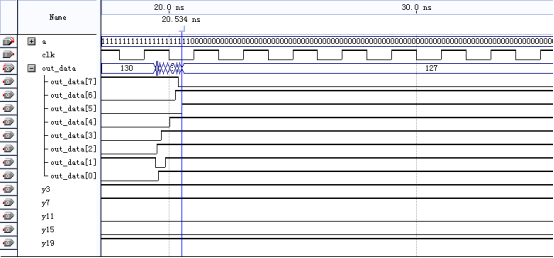

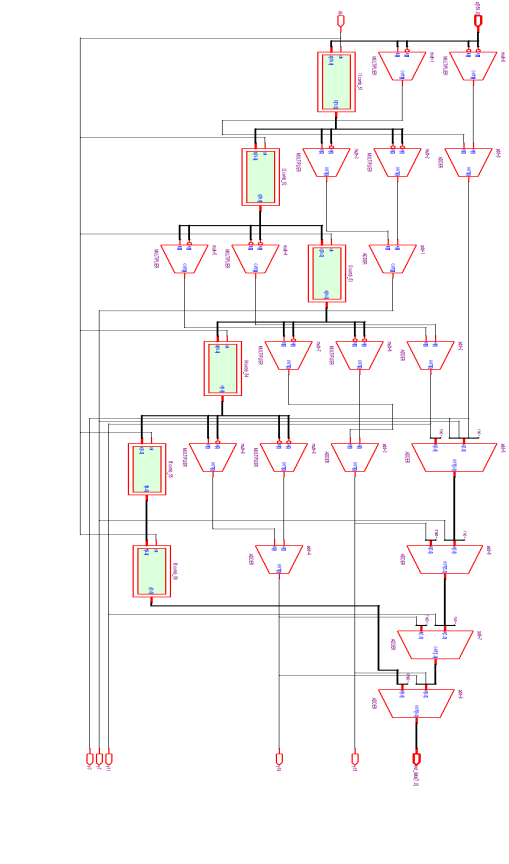

文中介绍了二分查找法的工作原理及帧同步的实现过程。在研究运算规则的同时,根据国际光互联论坛制定的甚短距离光传输标准对三种不同的查找方案进行了比较,最终选择二分查找法作为实践对象。其中,基本结构设计上采用了六级并行计算模式,再根据具体步骤制定帧同步的流程图,并以Altera公司开发的EDA工具QuartusII作为编译、仿真平台,完成了帧同步的硬件语言描述,从而达到了对数据结构中帧定界的查找目的。通过对仿真测试和对输出波形的理论分析,证明程序工作正常、方法行之有效,可以满足相关标准及使用要求,并在速度、准确率体现了二分查找算法的优越性。

关键字:帧定界;帧同步码;FPGA;甚短距离光传输

ABSTRACT

Along with the universality and developments of the network, the data’s delivering standards was also in the immediately continuous exaltation. This put forward the greater request on the control problem of the data. In digital signal, the data invariably existed with the structure of framer, and the each position of the time partition could be located with framer Delimitation. Therefore, in the digital connecting system, the framer’s synchronization was the most important part, and it included the creation and identification of the framer’s synchronization code.

The essay introduces working principle of the seeking law and the realization of frame synchronization. When research operation is regular, with the standard of very short reach which is made by optical international forum to compare the three different seeking schemes, eventually select the dividing-seeking is practice object. In which, on basic structural design has adopted 6 level parallel calculations pattern, establish the flow chart of frame synchronization again according to specific step, and with the EDA tool of Altera company's development Quartus II action compile and emulate platform, have completed the hardware language of framer synchronization describe, so have reached the delimiter seeking purpose in data structure. Through the emulation test and the theoretical analysis for export waveform, proof program work is normal , has effective method , can satisfy relative standard and use to ask , and has embodied the voluntarily optimize function in the process.

Key words: framer Delimitation;the framer’s synchronization code;FPGA;VSR

目 录

1 绪论 1

1.1 SDH与帧同步概述 1

1.2 FPGA现状与发展 2

1.3 论文内容介绍 3

2 帧同步 4

2.1 引言 4

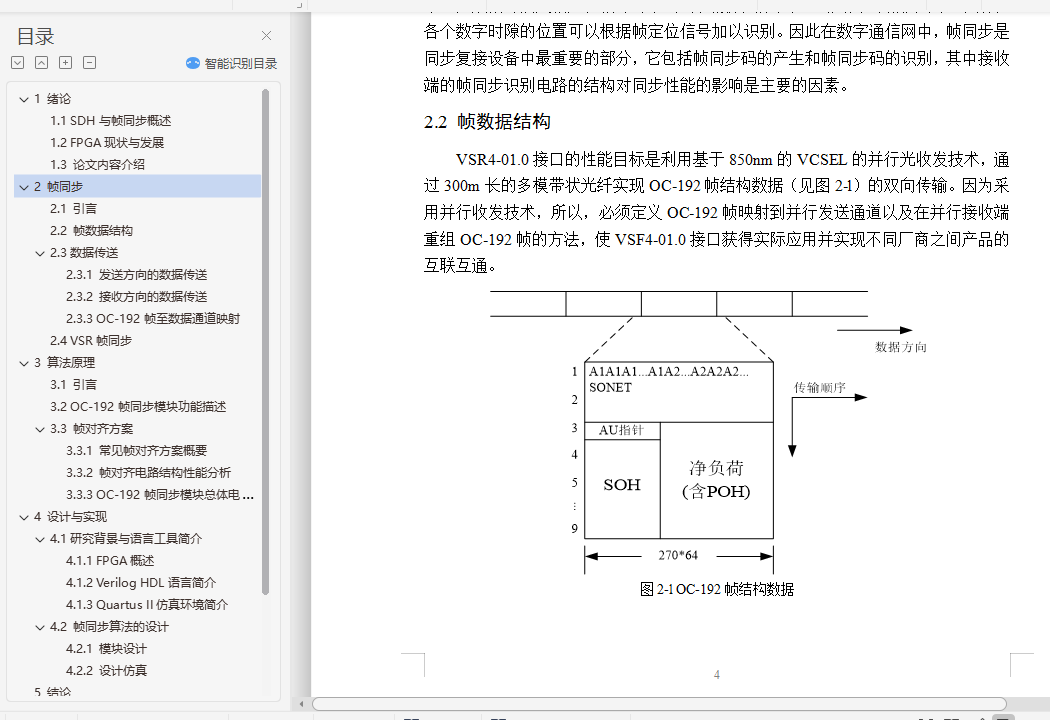

2.2 帧数据结构 4

2.3数据传送 5

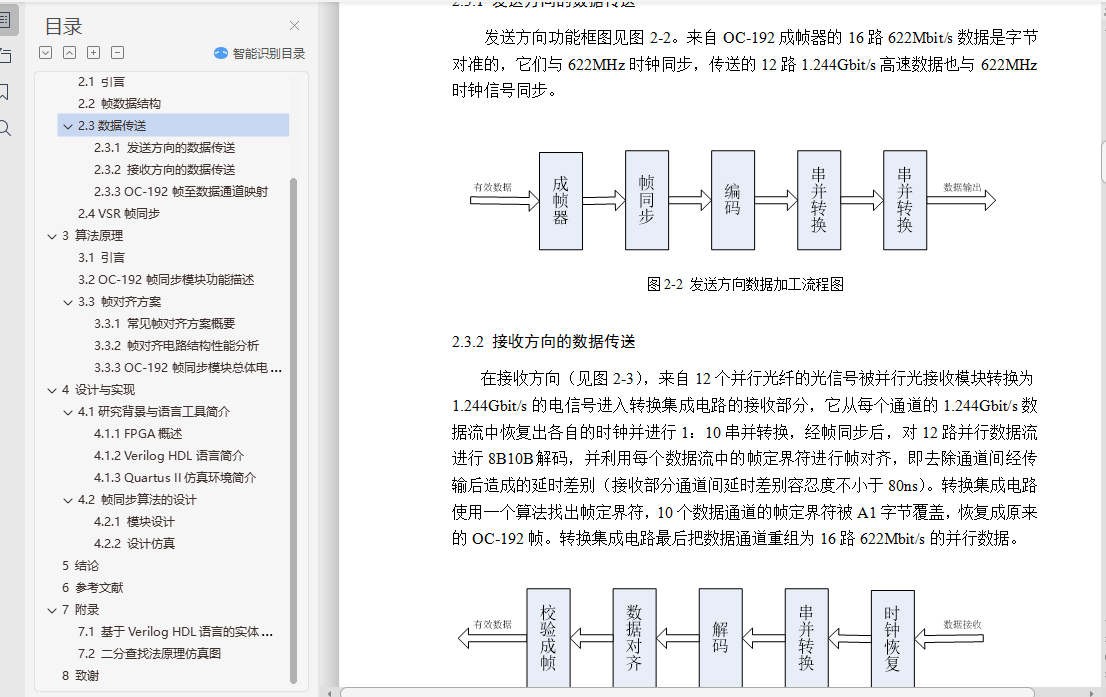

2.3.1 发送方向的数据传送 5

2.3.2 接收方向的数据传送 5

2.3.3 OC-192帧至数据通道映射 5

2.4 VSR帧同步 6

3 算法原理 8

3.1 引言 8

3.2 OC-192帧同步模块功能描述 8

3.3 帧对齐方案 8

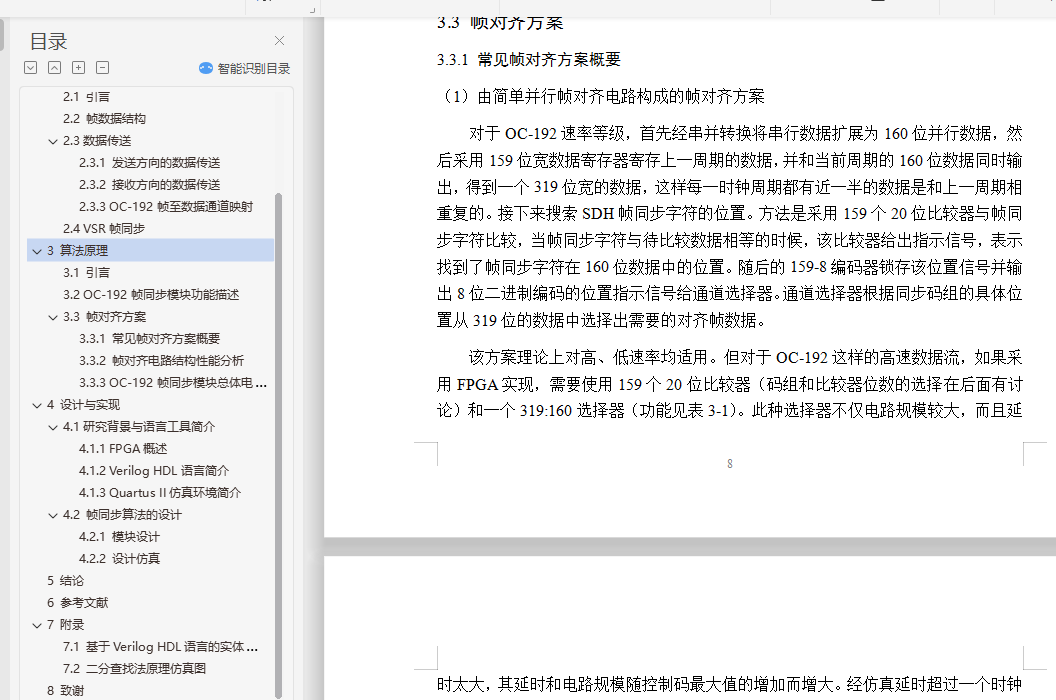

3.3.1 常见帧对齐方案概要 8

3.3.2 帧对齐电路结构性能分析 12

3.3.3 OC-192帧同步模块总体电路结构 12

4 设计与实现 13

4.1研究背景与语言工具简介 13

4.1.1 FPGA概述 13

4.1.2 Verilog HDL语言简介 13

4.1.3 Quartus II仿真环境简介 14

4.2 帧同步算法的设计 16

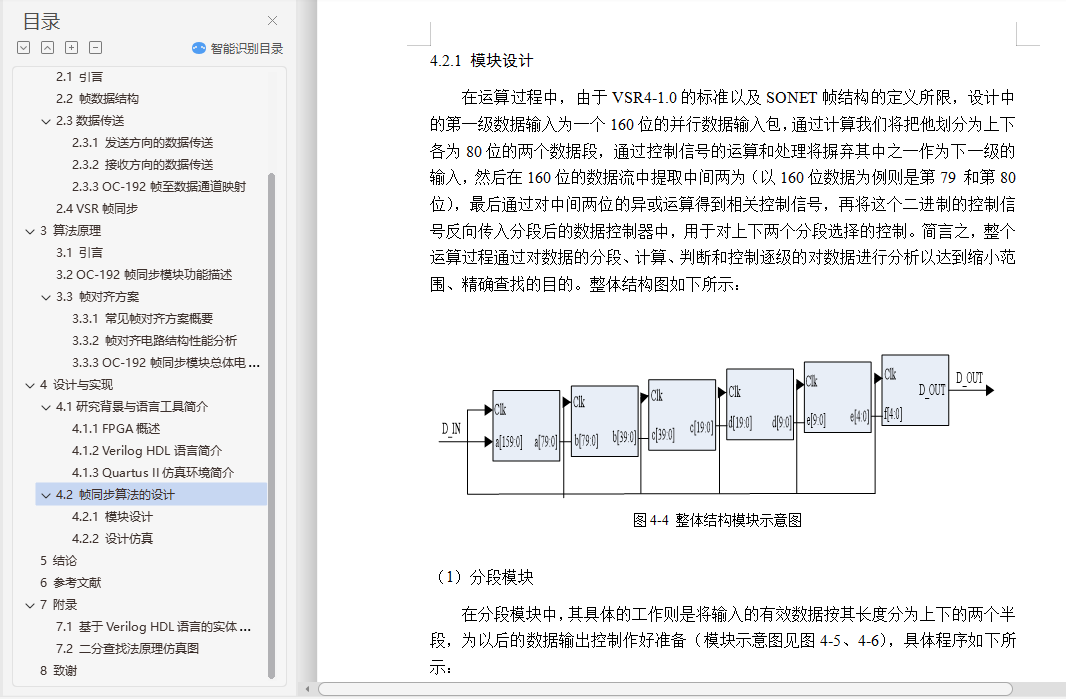

4.2.1 模块设计 17

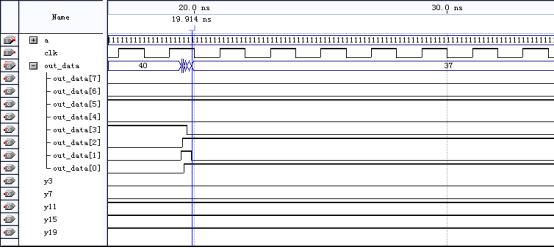

4.2.2 设计仿真 23

5 结论 26

6 参考文献 27

7 附录 28

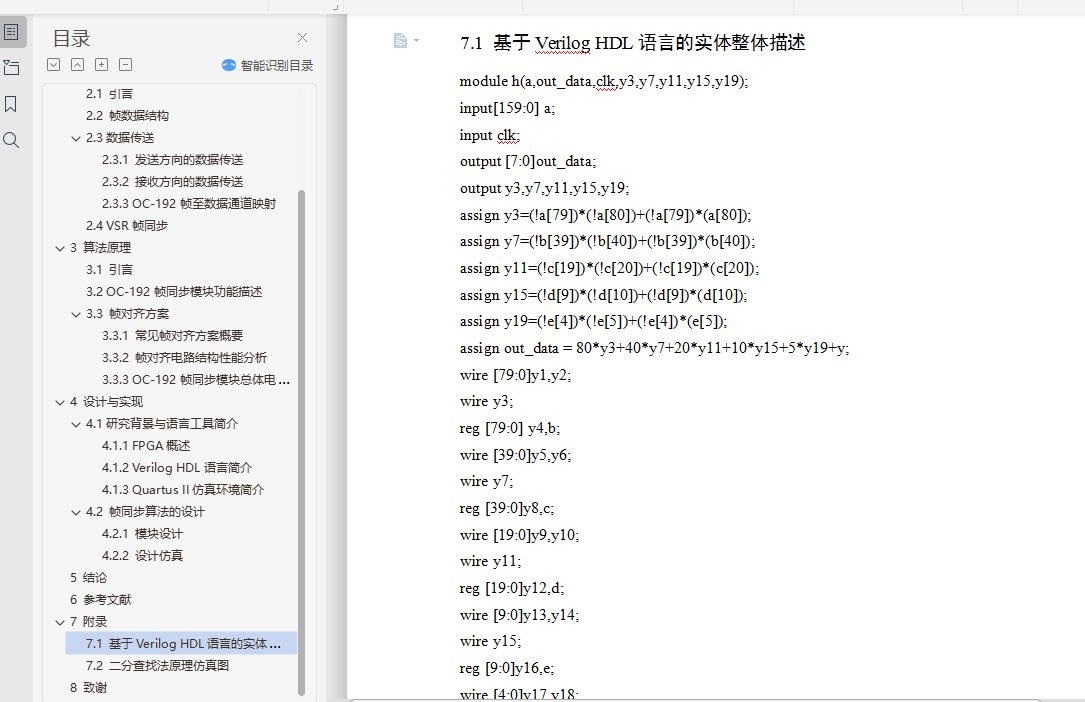

7.1 基于Verilog HDL语言的实体整体描述 28

7.2 二分查找法原理仿真图 34

8 致谢 35