摘 要

在通信系统中,数据在传输过程中,由于通道传输特性不理想,并且受到干扰或噪声的影响。分组码的消息验证码(CBC MAC)是一种最常用的信道编码方法,广泛应用于通信领域以提高数据传输的可靠性。随着半导体技术的迅速发展,在现代数字系统设计中,FPGA和CPLD的使用越来越广泛。与此同时,基于大规模可编程逻辑器件的EDA硬件解决方案也被广泛采用。

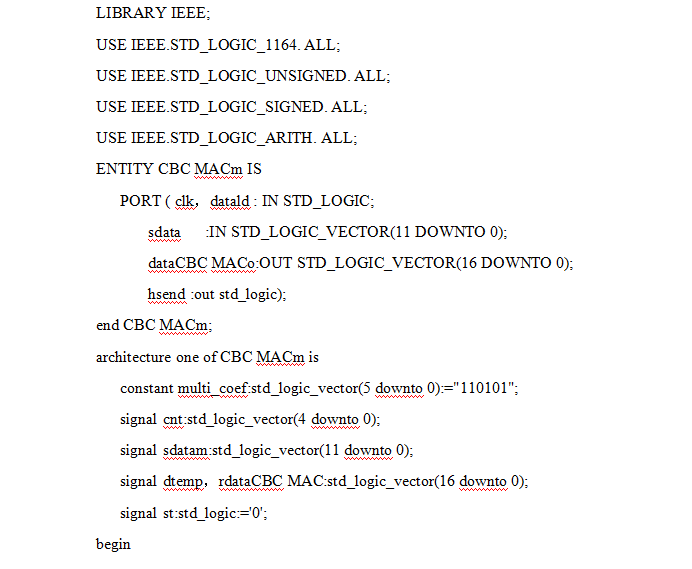

本文在上述背景下提出了基于FPGA的CBC MAC并行处理算法。采用VHDL语言实现了CBC MAC码的生成模块和校验模块,并以Altera公司开发的EDA工具QuartusⅡ8.0作为编译、仿真平台进行了仿真,最后将程序下载到CycloneⅢ芯片进行了验证测试。测试结果表明,算法的实验结果与理论分析结果完全相符。论文介绍了CBC MAC的编码、解码算法的工作原理以及FPGA技术、VHDL语言的基本知识,在此基础上详细介绍了在QuartusⅡ8.0中利用VHDL语言实现CBC MAC的过程。

关键词: 通信系统 CBC MAC FPGA VHDL

目 录

摘 要 I

1 绪论 1

1.1 课题研究背景和意义 1

1.2 课题研究现状 1

2 CBC MAC的特征和基本工作原理 2

2.1 CBC MAC的特征和码集选择的原则 2

2.2 CBC MAC生成原理 2

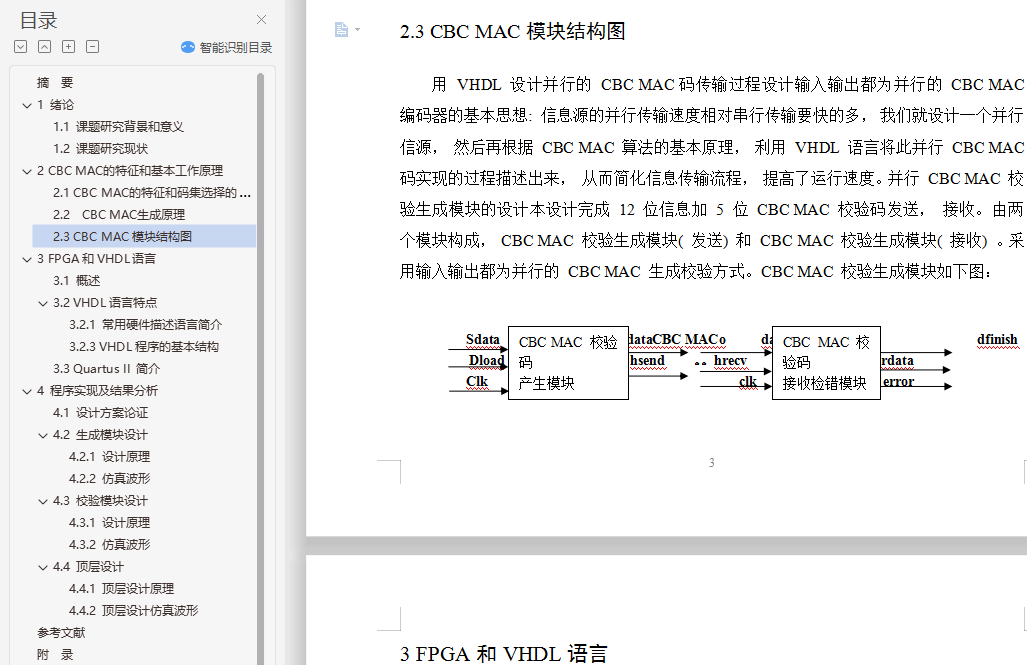

2.3 CBC MAC模块结构图 3

3 FPGA和VHDL语言 4

3.1 概述 4

3.2 VHDL语言特点 5

3.2.1 常用硬件描述语言简介 5

3.2.3 VHDL程序的基本结构 6

3.3 Quartus II 简介 6

4 程序实现及结果分析 8

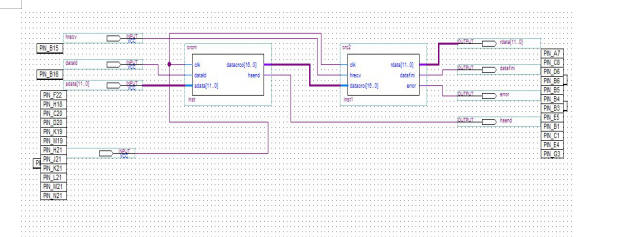

4.1 设计方案论证 8

4.2 生成模块设计 8

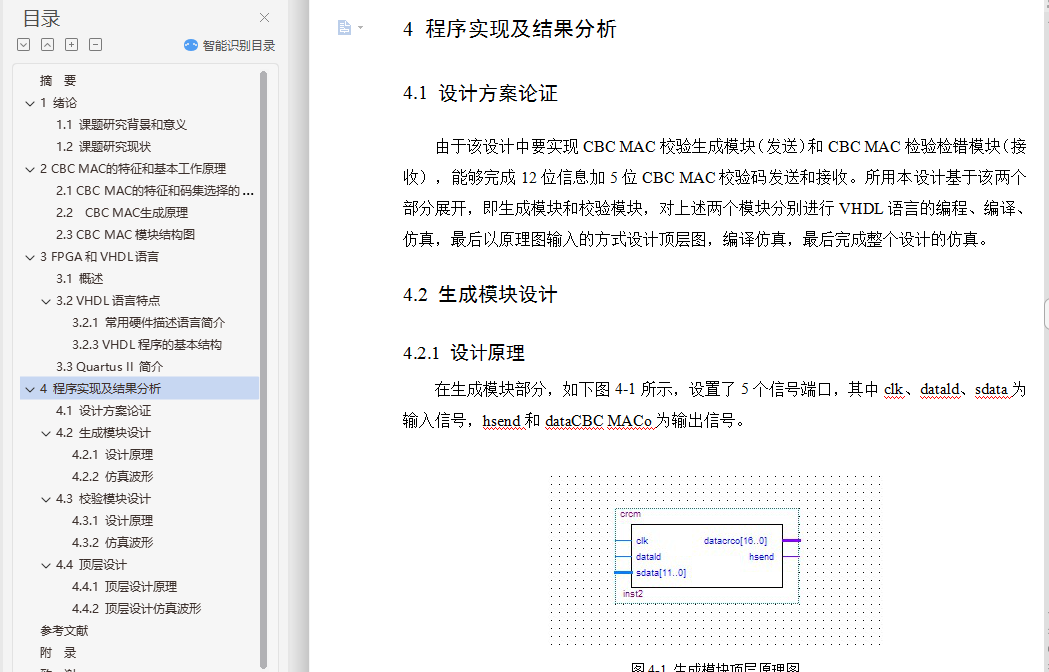

4.2.1 设计原理 8

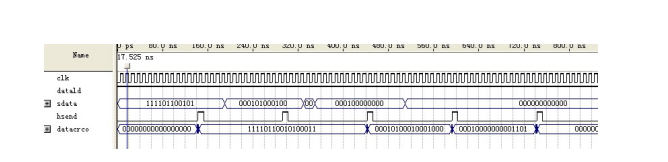

4.2.2 仿真波形 9

4.3 校验模块设计 9

4.3.1 设计原理 9

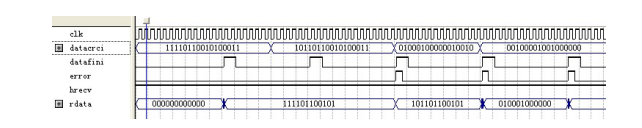

4.3.2 仿真波形 10

4.4 顶层设计 10

4.4.1 顶层设计原理 10

4.4.2 顶层设计仿真波形 11

参考文献 12

附 录 13

致 谢 16